Orodha ya maudhui:

- Mwandishi John Day day@howwhatproduce.com.

- Public 2024-01-30 12:51.

- Mwisho uliobadilishwa 2025-01-23 15:11.

Nimezidiwa na aina ya majibu ninayopata kwenye blogi hii. Asante watu kwa kutembelea blogi yangu na kunihamasisha kushiriki maarifa yangu na wewe. Wakati huu, nitawasilisha muundo wa moduli nyingine ya kupendeza tunayoona katika SOC zote - Mdhibiti wa Usumbufu.

Tutatengeneza Kidhibiti rahisi cha kukatiza kinachoweza kusanidiwa. Ni muundo unaoweza kusanidiwa kabisa na uliowekwa wazi ambao unaweza kusambazwa kwenye majukwaa yote. Niliunda hii baada ya kusoma mengi juu ya miundo mbinu maarufu ya usumbufu wa kudhibiti huko nje kama NVIC, 8259a, RISC-V PLIC, INTC ya Microblaze nk. Natumaini nyinyi mnaona blogi hii inasaidia na inakusaidia kupata ladha ya jinsi usumbufu unashughulikiwa na processor kwa msaada wa Mdhibiti wa Usumbufu.

Hatua ya 1: Maelezo

Zifuatazo ni maelezo ya IP:

- Kiolesura cha AHB3-Lite.

-

Vigezo vinavyoweza kusanidiwa vizuri:

- Idadi ya vyanzo vya usumbufu vya nje; inasaidia hadi kukatizwa kwa 63.

- Idadi ya viwango vya kipaumbele; inasaidia hadi viwango 63.

- Idadi ya viwango vya viota; inasaidia hadi kiwango cha 8 cha viota.

- Upana wa basi; 32 au 64.

- Ulimwengu na mitaa huweza kusumbuliwa.

- Kiwango cha kipaumbele kinachoweza kusanidiwa kwa kila kukatiza.

- Njia mbili za operesheni - Njia iliyokaliwa kikamilifu na Hali ya Kipaumbele Sawa.

- Inasaidia usumbufu nyeti wa kiwango cha juu.

Uainishaji wa RISC-V PLIC uliongozwa kukatiza utaratibu wa kupeana mikono hutumiwa katika muundo.

Kukatiza utayarishaji wa mapema kunahitajika kutoka 8259a

Masomo mengine: Microblaze INTC, NVIC

Hatua ya 2: Muhtasari wa PIC

Mdhibiti wa Usumbufu unaopangwa (PIC) hupokea usumbufu mwingi kutoka kwa vifaa vya nje na huunganisha kuwa pato moja la kukatiza kwa msingi wa processor.

PIC inadhibitiwa kupitia daftari za kudhibiti na hadhi. Rejista zote za PIC zimepangwa kwa kumbukumbu, na kupatikana kupitia kiolesura cha basi cha AHB3-Lite.

Benki ya rejista ina daftari la usanidi, wezesha rejista, rejista zinazosubiri, rejista za kazini, sajili za kipaumbele na rejista ya vitambulisho, ambazo ni kawaida kwa Wadhibiti wa Kukatiza.

Rejista ya usanidi hutumiwa kuweka hali ya utendaji wa PIC. Inaweza kufanya kazi kwa Njia iliyo Nested kikamilifu au Hali ya Kipaumbele Sawa.

Kila kukatiza kunaweza kupewa vipaumbele na kuficha kibinafsi. Ufichaji wa ulimwengu wa usumbufu wote pia unasaidiwa.

Benki ya rejista inaingiliana na Resolver ya Kipaumbele na BTC (Binary-Tree-Comparator) kutatua vipaumbele vya usumbufu unaosubiri na kudai kukatiza kwa processor ipasavyo. Rejista ya kitambulisho ina kitambulisho cha kipaumbele cha juu kinachosubiri kukatizwa.

Hatua ya 3: Ubunifu na Utekelezaji wa RTL

Mkazo wa muundo wa PIC juu ya kupunguza ucheleweshaji wa kutatua vipaumbele, ambayo ndio sehemu muhimu zaidi ya muundo. Kwa kuwa muundo unasuluhisha vipaumbele katika mzunguko wa saa moja, utendaji unapungua na kuongezeka kwa idadi ya vyanzo na ugumu wa Log2.

Ubunifu ulitekelezwa kwa mafanikio na muda uliothibitishwa hadi kufuata masafa kwenye Artix-7 FPGAs.

- Hadi vyanzo 15: 100 MHz

- Hadi vyanzo 63: 50 MHz

Usumbufu wa Usumbufu ulioongezwa na PIC peke yake ni mizunguko ya saa 3 (Ukiondoa wakati wa kubadili muktadha wa Prosesa na wakati wa kwanza wa kuleta maagizo ya ISR).

Hatua ya 4: Vidokezo Muhimu na Faili zilizoambatanishwa

Vidokezo Muhimu:

- Ikiwa interface ya AHB3-Lite haifai, unaweza kubadilisha moduli ya juu na utumie muundo wa mifupa wa PIC. Walakini benchi ya jaribio iliyotolewa ni ya IP na AHB3-Lite Interface.

- PIC IP v1.0 ni muundo rahisi wa RTL.

- Iliyothibitishwa kazini kufanya kazi kwa njia zote mbili.

Faili zilizoambatanishwa:

- Nambari za kubuni na benchi ya majaribio katika VHDL.

- Hati Kamili ya IP.

Ni muundo wa chanzo wazi… Jisikie huru kutumia…

Kwa maswali yoyote, wakati wowote:

Mitu Raj

Ilipendekeza:

Ubunifu wa Kidhibiti Rahisi cha Kuweka Cache cha Ushirika katika VHDL: Hatua 4

Ubunifu wa Kidhibiti Rahisi cha Kuweka Cache cha Ushirika katika VHDL: Katika agizo langu la awali, tuliona jinsi ya kubuni kidhibiti cha kache rahisi cha moja kwa moja. Wakati huu, tunasonga mbele. Tutatengeneza njia rahisi ya kuweka njia nne ya kidhibiti cha ushirika. Faida? Kiwango kidogo cha kukosa, lakini kwa gharama ya maelezo

Ubunifu wa Kidhibiti Rahisi cha Cache katika VHDL: Hatua 4

Ubunifu wa Kidhibiti Rahisi cha Cache katika VHDL: Ninaandika hii inayoweza kufundishwa, kwa sababu niliona ni ngumu kupata nambari ya kumbukumbu ya VHDL kujifunza na kuanza kubuni kidhibiti cha kache. Kwa hivyo niliunda kiboreshaji mwenyewe kutoka mwanzoni, na nikaijaribu kwa mafanikio kwenye FPGA. Nina p

Ubunifu wa Kidhibiti Rahisi cha VGA katika VHDL na Verilog: Hatua 5

Ubunifu wa Kidhibiti Rahisi cha VGA katika VHDL na Verilog: Katika hii inayoweza kufundishwa, tutabuni Mdhibiti rahisi wa VGA katika RTL. Mdhibiti wa VGA ni mzunguko wa dijiti iliyoundwa kutolea maonyesho ya VGA. Inasomeka kutoka kwa bafa ya Fremu (Kumbukumbu ya VGA) ambayo inawakilisha fremu inayoonyeshwa, na inazalisha nece

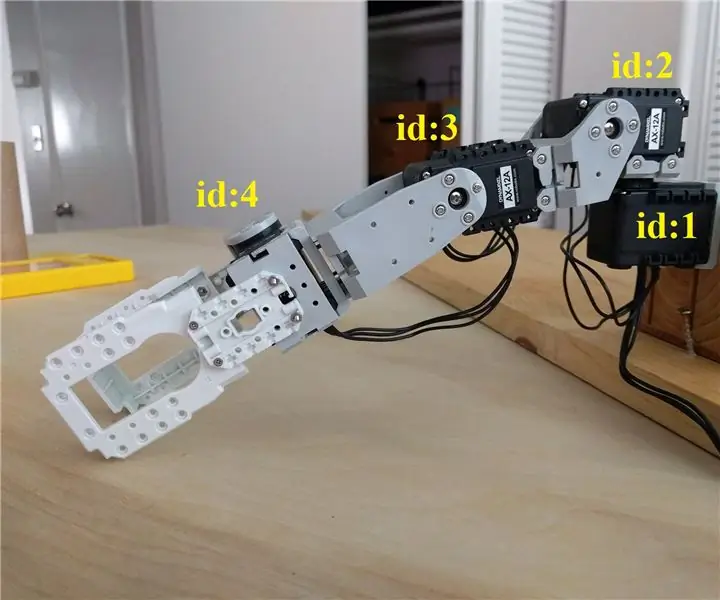

Chombo cha Roboti cha DIY kinachopangwa: Hatua 5

Chombo cha Roboti cha DIY kinachopangwa: Kwa nini Mradi huu: (a) Jifunze kudhibiti mkono wa roboti kwa kuandika nambari ya Python. Hii itakupa udhibiti wa punjepunje wakati unapoongeza programu ya kompyuta kwenye mkanda wako na kujifunza utendaji wa ndani wa motors za kisasa za rejista.

Kifurushi cha Betri cha Kidhibiti cha Xbox cha Mdhibiti kinachoweza kulipwa (mradi katika Maendeleo): Hatua 3 (na Picha)

DIY Xbox One Mdhibiti Kifurushi cha Battery kinachoweza kuchajiwa (mradi katika Maendeleo): Kabla hatujaingia kwenye maelezo ningependa kushughulikia kichwa. Mradi huu unaendelea kwa sababu ya matokeo kadhaa baada ya kujaribu muundo wa kwanza. Hiyo ikisemwa ninaunda bodi mpya ili kubeba mabadiliko ambayo nitapita. Nilifunua