Orodha ya maudhui:

- Mwandishi John Day day@howwhatproduce.com.

- Public 2024-01-30 12:51.

- Mwisho uliobadilishwa 2025-01-23 15:11.

Katika hii inayoweza kufundishwa, tutabuni Kidhibiti rahisi cha VGA katika RTL. Mdhibiti wa VGA ni mzunguko wa dijiti iliyoundwa kuendesha maonyesho ya VGA. Inasomeka kutoka kwa bafa ya fremu (Kumbukumbu ya VGA) ambayo inawakilisha fremu inayoonyeshwa, na hutoa data muhimu na ishara za usawazishaji kwa kusudi la kuonyesha.

Ikiwa unatafuta nambari ya Verilog / System verilog: Tembelea blogi yangu ya VGA Mdhibiti na Mfumo wa Video katika Verilog

Hatua ya 1: Muunganisho wa Mdhibiti wa VGA

Zifuatazo ni ishara kuu za kiolesura katika Kidhibiti cha VGA

- Saa ya Pixel au Saa ya VGA

- Ishara za HSYNC na VSYNC

Kwa onyesho la VGA lililochaguliwa, lazima kwanza uhesabu masafa ya Saa ya Pixel inayohitajika kuiendesha. Inategemea vigezo 3: Saizi Jumla za Usawa, Saizi za Wima Jumla, Kiwango cha Kuonyesha upya Screen.

Kwa kawaida, F = THP * TVP * Refresh Rate

Pata nyaraka kwenye saa ya pikseli inayohitajika kwa maonyesho anuwai ya VGA, kwenye RAR iliyoambatanishwa.

Ishara za HSYNC na VSYNC hutengenezwa kutoka saa ya Pixel. Wakati wa ishara za HSYNC na VSYNC hutegemea idadi ya vigezo: Usawa wa mbele na wima, Ukumbi wa nyuma na wima, Saizi za Ulalo na Uwima, Upana wa Polse ya Usawa na Usawa.

Vigezo hivi vimekadiriwa kwa onyesho la VGA iliyochaguliwa. Pata nyaraka hizi kwenye RAR iliyoambatanishwa.

Vigezo hivi ni vigezo vinavyoweza kusanidiwa katika IP yetu ya Mdhibiti wa VGA.

Hatua ya 2: Kuunganisha Mdhibiti wa VGA na Uonyesho wa VGA

Takwimu inaonyesha jinsi ya kuunganisha Mdhibiti wa VGA na onyesho la VGA. Unahitaji vifaa vingine viwili kukamilisha mfumo:

- Fremu bafa: Kumbukumbu ambayo inashikilia fremu kuonyeshwa.

- Video DAC: DAC inayobadilisha data ya dijiti ya RGB na inaendesha onyesho la VGA na ishara za Analog za RGB kwa kiwango kinachofaa cha voltage.

Moja ya DACs rahisi na maarufu ya Video ni ADV7125. Ni 8-bit DAC ambayo inabadilisha maneno ya dijiti ya RGB kuwa ishara za Analog 0-0.7 V na kuendesha onyesho la VGA.

Hatua ya 3: Muundo wa Bafa ya Sura

Ni kumbukumbu ambayo "huhifadhi" picha kuonyeshwa. Kwa kawaida ni RAM au wakati mwingine ROM. Tutazungumzia jinsi ya kuunda bafa ya fremu kuwakilisha picha. Fremu bafa hupitisha habari hii ya dijiti kwa Video DAC kwa amri kutoka kwa Mdhibiti wa VGA.

Kwanza tunapaswa kuamua kina cha pikseli kinachohitajika. Inaamua ubora wa picha, rangi anuwai pikseli inaweza kuwakilisha. Kwa DAC 8-bit, tunahitaji kuwakilisha vifaa vya msingi vya rangi ya pikseli: R, G, na B kwa vipande 8 kila moja. Inamaanisha, pikseli ni ya 24-bit.

Kila pikseli huhifadhiwa kwa njia inayofanana katika maeneo ya kumbukumbu ya Bafa ya Sura.

Tuseme picha inayoonyeshwa ni saizi 800x600.

Kwa hivyo Frefa bafa inahitajika ni 800x600 = 480000 x 24 bits kumbukumbu

Ukubwa wa jumla ya kumbukumbu ni 800x600x24 = 1400 kB takriban.

Ikiwa picha nyeusi na nyeupe, 800x600x1 = 60 kB approx.

Kuzuia RAM labda kutumika kutumiwa bafa ya fremu katika Xilinx FPGAs.

Hatua ya 4: Vidokezo

- Ishara za ziada zinahitajika kwa Mdhibiti wa VGA kulingana na DAC iliyochaguliwa. Nimetumia ADV7125.

- Ongeza ucheleweshaji wa mzunguko kupitia flip-flops kwenye VSYNC na HSYNC kabla ya kuendesha onyesho la VGA. Hii ni kwa sababu ya latency za DAC na Kumbukumbu. Ishara za pikseli zinapaswa kusawazishwa na HSYNC na VSYNC. Kwa upande wangu, ilikuwa kucheleweshwa kwa mzunguko 2.

- Ikiwa bafa ya fremu ya ukubwa uliopewa haiwezi kubuniwa kwenye FPGA kwa sababu ya kuzuia upeo wa ukubwa wa kondoo-dume, tumia kumbukumbu ndogo kuwakilisha picha na hariri tu msimbo ili kusonga juu ya anwani kwenye mpaka wa kumbukumbu inayopatikana, badala ya mpaka kamili wa fremu. Hii itaiga picha sawa tena na tena kwenye skrini nzima. Njia nyingine ni kuongeza pikseli ambayo kila pikseli imeigwa ili kuonyesha picha nzima katika skrini kamili, kwa azimio kidogo. Hii inaweza kufanywa kwa kurekebisha mantiki ya nyongeza ya anwani kwenye nambari.

- IP inabebeka kabisa kwa FPGA zote na inathibitisha hadi 100 MHz kwenye Virtex-4 FPGA.

Hatua ya 5: Faili zilizoambatanishwa

RAR ina:

- Nambari ya Mdhibiti wa VGA

- PDF za viwango vya VGA.

Ilipendekeza:

Ubunifu wa Kidhibiti Rahisi cha Kuweka Cache cha Ushirika katika VHDL: Hatua 4

Ubunifu wa Kidhibiti Rahisi cha Kuweka Cache cha Ushirika katika VHDL: Katika agizo langu la awali, tuliona jinsi ya kubuni kidhibiti cha kache rahisi cha moja kwa moja. Wakati huu, tunasonga mbele. Tutatengeneza njia rahisi ya kuweka njia nne ya kidhibiti cha ushirika. Faida? Kiwango kidogo cha kukosa, lakini kwa gharama ya maelezo

Ubunifu wa Kidhibiti cha Kukatiza kinachopangwa katika VHDL: Hatua 4

Ubunifu wa Mdhibiti wa Kukatiza unaoweza kupangwa katika VHDL: Nimezidiwa na aina ya majibu ninayopata kwenye blogi hii. Asante watu kwa kutembelea blogi yangu na kunihamasisha kushiriki maarifa yangu na wewe. Wakati huu, nitawasilisha muundo wa moduli nyingine ya kupendeza tunayoiona katika SOC zote - Kukatiza C

Ubunifu wa Kidhibiti Rahisi cha Cache katika VHDL: Hatua 4

Ubunifu wa Kidhibiti Rahisi cha Cache katika VHDL: Ninaandika hii inayoweza kufundishwa, kwa sababu niliona ni ngumu kupata nambari ya kumbukumbu ya VHDL kujifunza na kuanza kubuni kidhibiti cha kache. Kwa hivyo niliunda kiboreshaji mwenyewe kutoka mwanzoni, na nikaijaribu kwa mafanikio kwenye FPGA. Nina p

Kifurushi cha Betri cha Kidhibiti cha Xbox cha Mdhibiti kinachoweza kulipwa (mradi katika Maendeleo): Hatua 3 (na Picha)

DIY Xbox One Mdhibiti Kifurushi cha Battery kinachoweza kuchajiwa (mradi katika Maendeleo): Kabla hatujaingia kwenye maelezo ningependa kushughulikia kichwa. Mradi huu unaendelea kwa sababu ya matokeo kadhaa baada ya kujaribu muundo wa kwanza. Hiyo ikisemwa ninaunda bodi mpya ili kubeba mabadiliko ambayo nitapita. Nilifunua

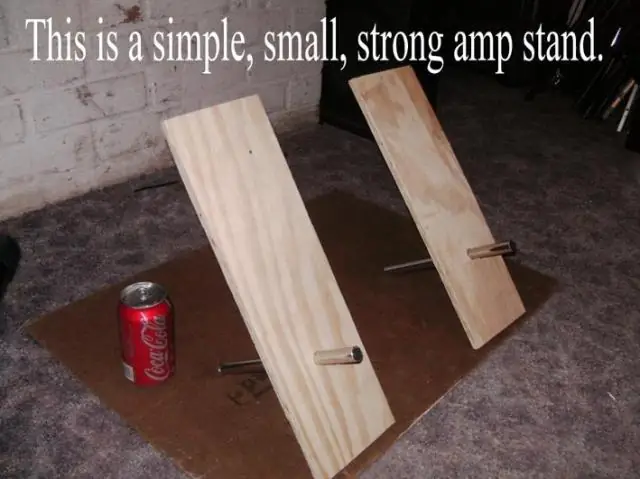

Simama ya Gitaa Amp Tilt - Ubunifu wa "Kiti cha Kiafrika" - Rahisi, Ndogo, Nguvu, Rahisi, Bure au Nafuu Halisi: Hatua 9

Simama ya Gitaa Amp Tilt - Ubunifu wa "Kiti cha Kiafrika" - Rahisi, Ndogo, Nguvu, Rahisi, Bure au Nafuu Halisi: Gitaa Amp Tilt Simama - Rahisi sana - rahisi, ndogo, nguvu, bure au bei rahisi. Kwa amps zote za saizi, hata kabati kubwa zilizo na kichwa tofauti. Tengeneza tu bodi na mabomba ukubwa na unahitaji kwa karibu vifaa vyovyote unavyotaka