Orodha ya maudhui:

- Mwandishi John Day day@howwhatproduce.com.

- Public 2024-01-30 12:51.

- Mwisho uliobadilishwa 2025-01-23 15:11.

Ninaandika hii inayoweza kufundishwa, kwa sababu niliona ni ngumu kupata nambari ya kumbukumbu ya VHDL ya kujifunza na kuanza kubuni kidhibiti cha cache. Kwa hivyo niliunda kiboreshaji mwenyewe kutoka mwanzoni, na nikaijaribu kwa mafanikio kwenye FPGA. Nimewasilisha kidhibiti rahisi cha moja kwa moja cha ramani hapa, na vile vile nimeunda Mfumo mzima wa Usindikaji-Kumbukumbu ili kujaribu Mdhibiti wa Cache. Natumai nyinyi mnaona hii inafaa kufundisha kama kumbukumbu ya kubuni vidhibiti vyako vya kashe.

Hatua ya 1: Maelezo

Hizi ndio sifa kuu za Mdhibiti wa kache tutakayounda:

- Ramani ya moja kwa moja. (nenda kwenye kiunga hiki ikiwa unatafuta Mdhibiti wa Cache ya Ramani ya Ushirika)

- Benki moja, Inazuia Cache.

- Sera ya Kuandika-Kupitia maandishi ya Andika.

- Hakuna-Andika kutenga au Andika Kuzunguka Sera juu ya Kukosa kuandika.

- Hakuna Kuandika bafa au uboreshaji mwingine.

- Array ya Tag imejumuishwa.

Mbali na hilo, tutatengeneza Kumbukumbu ya Cache na Mfumo wa Kumbukumbu Kuu pia.

Maelezo ya msingi (yanayoweza kusanidiwa) ya Kumbukumbu ya Cache:

- Kache 256 za Benki Moja.

- Mistari ya Cache 16, kila Line Cache (Block) = 16 Byte.

Maelezo ya Kumbukumbu kuu:

- Synchronous Soma / Andika Kumbukumbu.

- Kumbukumbu iliyoingiliwa na benki nyingi - benki nne za kumbukumbu.

- Kila saizi ya benki = 1 kB kila moja. Kwa hivyo, jumla ya ukubwa = 4 kB.

- Neno (4 Baiti) kumbukumbu inayoweza kushughulikiwa na Basi ya Anwani 10-bit.

- Upeo wa juu wa kusoma. Soma Upana wa Takwimu = 16 Baiti katika mzunguko wa saa moja.

- Andika Upana wa Takwimu = 4 Baiti.

KUMBUKA: angalia maagizo yangu mapya ikiwa unatafuta muundo wa kidhibiti cha kashe cha njia nne

Hatua ya 2: Mtazamo wa RTL wa Mfumo Mzima

Uwakilishi kamili wa RTL wa Moduli ya Juu umeonyeshwa kwenye Kielelezo (ukiondoa processor). Chaguo-msingi za mabasi ni:

- Basi zote za Takwimu ni Basi 32-bit.

- Anwani ya Bus = 32-bit Bus (Lakini ni bits 10 tu zinazoweza kushughulikiwa hapa na Kumbukumbu).

- Kuzuia Takwimu = bits 128 (Bus pana ya Bandwidth kwa Soma).

- Vipengele vyote vinaendeshwa na saa sawa.

Hatua ya 3: Mazingira ya Mtihani

Moduli ya Juu ilijaribiwa kwa kutumia Benchi ya Mtihani, ambayo inaunda tu Prosesa isiyo na bomba (Kwa sababu kubuni processor nzima sio rahisi kabisa !!). Benchi ya Mtihani hutengeneza maombi ya Soma / Andika Takwimu kwa Kumbukumbu mara kwa mara. Hii inadhihaki maagizo ya kawaida ya "Mzigo" na "Hifadhi", kawaida katika programu zote zilizotekelezwa na processor. Matokeo ya majaribio yalithibitisha ufanisi wa Mdhibiti wa Cache. Zifuatazo ni takwimu za mtihani zilizozingatiwa:

- Ishara zote za Soma / Andika Miss na Hit zilitengenezwa kwa usahihi.

- Shughuli zote za Kusoma / Kuandika Data zilifanikiwa.

- Hakuna shida za utangamano wa data / kutofautiana zilizogunduliwa.

- Ubunifu ulithibitishwa kwa muda mzuri kwa Maxm. Mzunguko wa saa ya kazi = 110 MHz katika Xilinx Virtex-4 ML-403 Bodi (mfumo mzima), 195 MHz kwa Mdhibiti wa Cache peke yake.

- Kuzuia RAM zilifikiriwa kwa Kumbukumbu kuu. Safu zingine zote zilitekelezwa kwenye LUTs.

Hatua ya 4: Faili zilizoambatanishwa

Faili zifuatazo zimeambatanishwa hapa na blogi hii:

- Faili za. VHD za Mdhibiti wa Cache, Mpangilio wa Takwimu za Cache, Mfumo wa Kumbukumbu kuu.

- Benchi la Mtihani.

- Nyaraka kwenye Kidhibiti cha Cache.

Vidokezo:

- Pitia nyaraka kwa uelewa kamili wa uainishaji wa Mdhibiti wa kache uliowasilishwa hapa.

- Mabadiliko yoyote katika nambari yanategemea moduli zingine. Kwa hivyo, mabadiliko yanapaswa kufanywa kwa busara. Zingatia maoni na vichwa vyote ambavyo nimetoa.

- Ikiwa kwa sababu yoyote, Zuia RAM hazizingatiwi Kumbukumbu kuu, PUNGUZA saizi ya kumbukumbu, ikifuatiwa na mabadiliko katika upana wa basi ya anwani kwenye faili na kadhalika. Ili kumbukumbu hiyo hiyo iweze kutekelezwa ama kwenye LUTs au RAM iliyosambazwa. Hii itaokoa wakati na rasilimali. Au, Nenda kwa nyaraka maalum za FPGA na upate nambari inayofaa ya Kuzuia RAM na uhariri nambari ipasavyo, na utumie maelezo sawa ya upana wa basi. Mbinu sawa kwa Altera FPGAs.

Ilipendekeza:

Ubunifu wa Kidhibiti Rahisi cha Kuweka Cache cha Ushirika katika VHDL: Hatua 4

Ubunifu wa Kidhibiti Rahisi cha Kuweka Cache cha Ushirika katika VHDL: Katika agizo langu la awali, tuliona jinsi ya kubuni kidhibiti cha kache rahisi cha moja kwa moja. Wakati huu, tunasonga mbele. Tutatengeneza njia rahisi ya kuweka njia nne ya kidhibiti cha ushirika. Faida? Kiwango kidogo cha kukosa, lakini kwa gharama ya maelezo

Ubunifu wa Kidhibiti cha Kukatiza kinachopangwa katika VHDL: Hatua 4

Ubunifu wa Mdhibiti wa Kukatiza unaoweza kupangwa katika VHDL: Nimezidiwa na aina ya majibu ninayopata kwenye blogi hii. Asante watu kwa kutembelea blogi yangu na kunihamasisha kushiriki maarifa yangu na wewe. Wakati huu, nitawasilisha muundo wa moduli nyingine ya kupendeza tunayoiona katika SOC zote - Kukatiza C

Ubunifu wa Kidhibiti Rahisi cha VGA katika VHDL na Verilog: Hatua 5

Ubunifu wa Kidhibiti Rahisi cha VGA katika VHDL na Verilog: Katika hii inayoweza kufundishwa, tutabuni Mdhibiti rahisi wa VGA katika RTL. Mdhibiti wa VGA ni mzunguko wa dijiti iliyoundwa kutolea maonyesho ya VGA. Inasomeka kutoka kwa bafa ya Fremu (Kumbukumbu ya VGA) ambayo inawakilisha fremu inayoonyeshwa, na inazalisha nece

Kifurushi cha Betri cha Kidhibiti cha Xbox cha Mdhibiti kinachoweza kulipwa (mradi katika Maendeleo): Hatua 3 (na Picha)

DIY Xbox One Mdhibiti Kifurushi cha Battery kinachoweza kuchajiwa (mradi katika Maendeleo): Kabla hatujaingia kwenye maelezo ningependa kushughulikia kichwa. Mradi huu unaendelea kwa sababu ya matokeo kadhaa baada ya kujaribu muundo wa kwanza. Hiyo ikisemwa ninaunda bodi mpya ili kubeba mabadiliko ambayo nitapita. Nilifunua

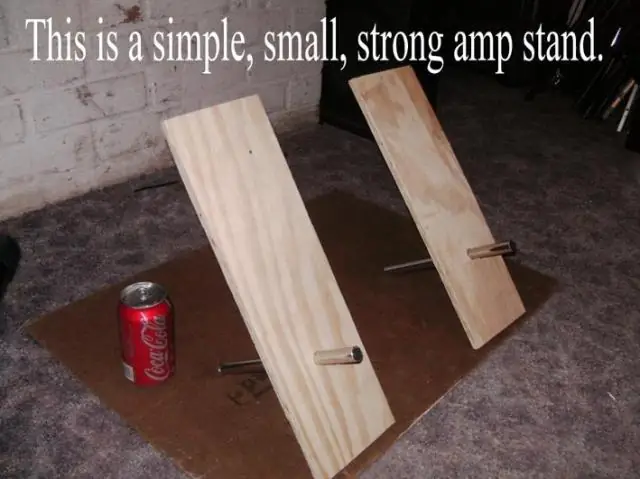

Simama ya Gitaa Amp Tilt - Ubunifu wa "Kiti cha Kiafrika" - Rahisi, Ndogo, Nguvu, Rahisi, Bure au Nafuu Halisi: Hatua 9

Simama ya Gitaa Amp Tilt - Ubunifu wa "Kiti cha Kiafrika" - Rahisi, Ndogo, Nguvu, Rahisi, Bure au Nafuu Halisi: Gitaa Amp Tilt Simama - Rahisi sana - rahisi, ndogo, nguvu, bure au bei rahisi. Kwa amps zote za saizi, hata kabati kubwa zilizo na kichwa tofauti. Tengeneza tu bodi na mabomba ukubwa na unahitaji kwa karibu vifaa vyovyote unavyotaka