Orodha ya maudhui:

- Mwandishi John Day day@howwhatproduce.com.

- Public 2024-01-30 12:49.

- Mwisho uliobadilishwa 2025-01-23 15:11.

Na AmCoderhttps://www.linkedin.com/in/mitu Fuata Zaidi na mwandishi:

Kuhusu: Mitu Raj - Mtu wa kupendeza tu na Mwanafunzi - Mbuni wa Chip - Msanidi programu - Fizikia na Mpenda shauku zaidi kuhusu AmCoder »

## Hiki ni kiunga kilichobofiwa zaidi, maarufu katika Google kwa utekelezaji wa VHDL wa CORDIC ALGORITHM ili kutengeneza wimbi la sine na cosine ## Kwa sasa, algorithms nyingi zenye ufanisi wa vifaa zipo, lakini hizi hazijulikani sana kwa sababu ya utawala wa mifumo ya programu. miaka mingi. CORDIC ni algorithm kama hiyo ambayo sio chochote isipokuwa seti ya mabadiliko na kuongeza mantiki inayotumika kwa kuhesabu anuwai ya kazi pamoja na kazi fulani za trigonometric, hyperbolic, linear na logarithmic. Hii ndio algorithm inayotumiwa katika mahesabu n.k. Kwa hivyo kwa kutumia tu shifters rahisi na viboreshaji tunaweza kubuni vifaa na utata mdogo lakini nguvu ya DSP kutumia algorithm ya ujanja. Kwa hivyo inaweza kutengenezwa kama muundo wazi wa RTL katika VHDL au Verilog bila kutumia vitengo vyovyote vya kuelea au IPs tata za hesabu.

Hatua ya 1: VHDL na Modelsim

Hapa algorithm ya kitendawili inatekelezwa kwa kutumia VHDL kutengeneza wimbi la sine na wimbi la cose. Inaweza kutoa sine na cosine ya pembe ya pembejeo kwa usahihi mkubwa. Nambari ni synthesizable kwenye FPGA. Modelsim hutumiwa kuiga muundo na benchi ya jaribio.

Hatua ya 2: Nambari ya VHDL ya Ubuni na Benchi la Mtihani

Miongozo ----

Mbinu ya kuongeza binary hutumiwa kuwakilisha nambari za uhakika zinazoelea.

Tafadhali nenda kwenye hati zilizoambatanishwa kabla ya kuweka nambari.

Nenda kwa njia ya Kuiga cordic_v4.vhd - Ubunifu -Uingizo ni pembe katika bits 32 + ishara kidogo; inaweza kusindika pembe yoyote kutoka 0 hadi +/- digrii 360 na usahihi wa pembejeo wa digrii 0.000000000233. Wakati wa kutoa pembejeo -> MSB ni ishara kidogo na alama zingine 32 zinawakilisha ukubwa. -Pato la muundo ni sine yake na thamani ya cos katika bits 16 + ishara kidogo.ie; kwa usahihi 0.00001526. Tafadhali kumbuka kuwa pato linaonyeshwa katika fomu ya kupongeza ya 2 ikiwa sine husika au thamani ya cos ni hasi. Kuiga testb.vhd - Mtihani wa Benchi ya Ubunifu (1) pembe za kuingiza na kuvuta upya = '0'. Baada ya hatua mbili za simulation vuta upya kuwa '1' na "endesha zote". (2) Katika dirisha la kuiga weka radi ya dhambi na ishara za cos kama desimali na fomati> Analog (otomatiki). (3) Zungusha ili uone umbile vizuri.

Hatua ya 3: Faili zimeambatishwa

(1) cordic_v4.vhd - Ubunifu. (2) testb.vhd - Jaribio la benchi la muundo.

(3) Hati juu ya jinsi ya kulazimisha pembejeo za pembe na kubadilisha matokeo ya binary.

Sasisho: JAWABU HIZI ZINA UWEZO NA HAZITOLEWI TENA. TAFADHALI TUMIA MAFUTA KUTOKA HATUA INAYOFUATA

Hatua ya 4: Mini-Cordic IP Core - 16 Bit

Upeo wa utekelezaji hapo juu ni polepole, chini ya mzunguko wa saa kwa sababu ya kufanya hesabu katika mzunguko wa saa moja.

- Njia muhimu zinazosambazwa kwa mizunguko mingi ili kuboresha utendaji. ya awali. Testbench:

otomatiki kabisa kutoka pembejeo za pembe 0 hadi 360

Faili zilizoambatanishwa: 1) mini ndogo ya faili ndogo ya vhdl2) benchi ndogo ya jaribio la mini3) Mini Cordic IP Core mwongozo4) Hati juu ya jinsi ya kulazimisha pembe na kubadilisha matokeo

Kwa maswali yoyote, jisikie huru kuwasiliana nami:

Mitu Raj

nifuate:

barua: iammituraj@gmail.com

### Jumla ya upakuaji: 325 hadi 01-05-2021 ###

# # # Msimbo wa mwisho kuhaririwa: Julai-07-2020 ###

Ilipendekeza:

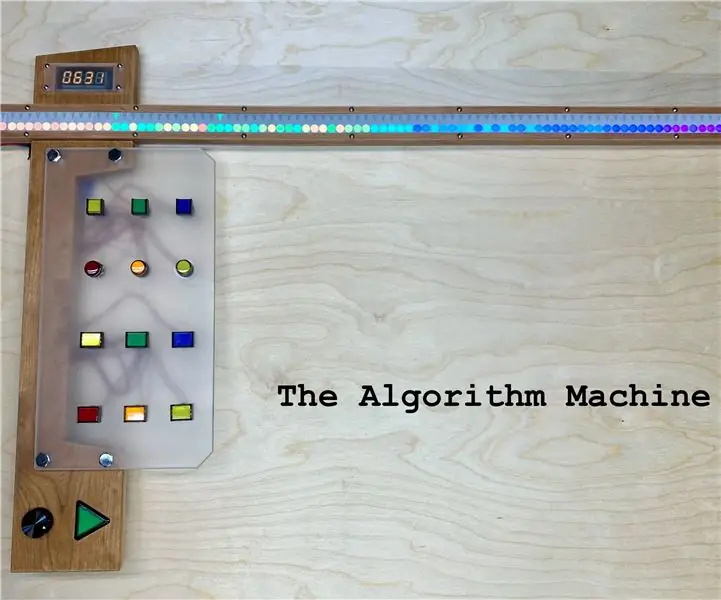

Mashine ya Algorithm: Hatua 13 (na Picha)

Mashine ya Algorithm: Nimekuwa nikifundisha sayansi ya kompyuta katika kiwango cha vyuo vikuu kwa miaka 15, na ingawa utaalam wangu uko zaidi upande wa programu, bado ninatumia muda mwingi kufunika algorithms za kawaida za kutafuta na kuchagua. Kutoka kwa mtazamo wa kufundisha

Mchezo wa Bodi Akili ya bandia: algorithm ya Minimax: Hatua 8

Mchezo wa Bodi ya Akili ya bandia: Algorithm ya Minimax: Umewahi kujiuliza jinsi kompyuta unazocheza dhidi ya chess au checkers zinafanywa? Usiangalie zaidi ya hii inayoweza kufundishwa kwani itakuonyesha jinsi ya kutengeneza akili rahisi lakini nzuri ya bandia (AI) ukitumia Minimax Algorithm! Kwa kutumia th

Kujisawazisha Roboti Kutumia PID Algorithm (STM MC): Hatua 9

Kujisawazisha Roboti Kutumia PID Algorithm (STM MC): Hivi karibuni kazi nyingi imefanywa katika usawazishaji wa vitu. Wazo la usawa wa kibinafsi lilianza na usawazishaji wa pendulum iliyogeuzwa. Dhana hii iliongezwa hadi muundo wa ndege pia. Katika mradi huu, tumebuni mod ndogo

Tic Tac Toe juu ya Arduino Pamoja na AI (Minimax Algorithm): 3 Hatua

Tic Tac Toe juu ya Arduino na AI (Minimax Algorithm): Katika hii Inayoweza kufundishwa nitakuonyesha jinsi ya kujenga mchezo wa Tic Tac Toe na AI ukitumia Arduino. Unaweza kucheza dhidi ya Arduino au uangalie Arduino ikicheza dhidi yake. Ninatumia algorithm inayoitwa " minimax algorithm "

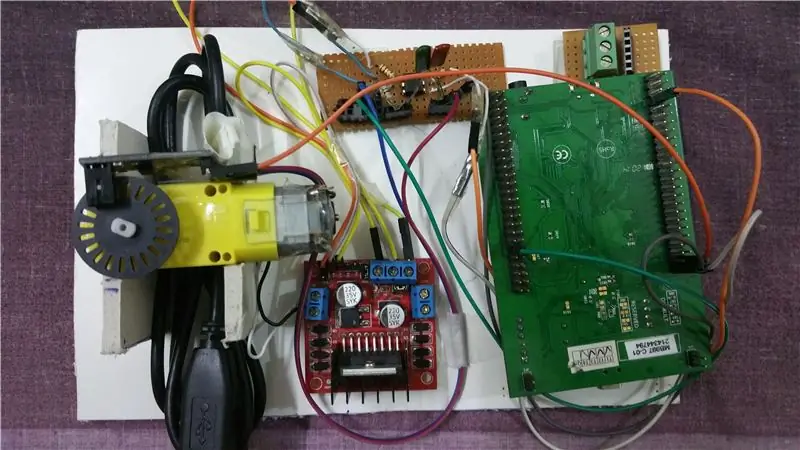

Udhibiti wa kasi wa Magari ya DC Kutumia PID Algorithm (STM32F4): Hatua 8 (na Picha)

Udhibiti wa kasi wa Magari ya DC Kutumia Algorithm ya PID (STM32F4): hello kila mtu, Hii ni tahir ul haq na mradi mwingine. Wakati huu ni STM32F407 kama MC. Huu ni mwisho wa mradi wa muhula wa katikati. Natumahi unaipenda.Inahitaji dhana nyingi na nadharia ili tuingie ndani kwanza.Na ujio wa kompyuta na