Orodha ya maudhui:

- Hatua ya 1: Kuunda Moduli ya PWM- Faili Chanzo

- Hatua ya 2: Kuunda Moduli ya PWM- Usanidi wa Vivado

- Hatua ya 3: Kuunda Moduli ya PWM- Unda Faili ya Mradi

- Hatua ya 4: Kuunda Moduli ya PWM- Kubuni Kubuni na Kuweka Picha Kizuizi (I)

- Hatua ya 5: Kuunda Moduli ya PWM- Kubuni Kubuni na Kuweka Picha Kizuizi (II)

- Hatua ya 6: Kuunda Moduli ya PWM- Kubuni Ubunifu na Kuweka Picha Kizuizi (III)

- Hatua ya 7: Kuunda Moduli ya PWM- Kubuni Ubunifu na Kuweka Picha Kizuizi (IV)

- Hatua ya 8: Kuunda Moduli ya PWM- Kubuni Kubuni na Kuweka Picha Kizuizi (V)

- Hatua ya 9: Kuunda Moduli ya PWM- Ufungaji wa vifaa

- Hatua ya 10: Kuunda Moduli ya PWM- Kuzalisha Bitstream na kuzindua SDK

- Hatua ya 11: Kuunda Moduli ya PWM- Unda Programu mpya katika Xilinx SDK

- Hatua ya 12: Kuunda Moduli ya PWM- Muhtasari wa Mradi wa Kugundua (I)

- Hatua ya 13: Kuunda Moduli ya PWM- Muhtasari wa Mradi wa Kugundua (II)

- Hatua ya 14: Kuunda Moduli ya PWM- Muhtasari wa Mtafiti wa Mradi (III)

- Hatua ya 15: Kuunda Moduli ya PWM- Funga Kazi ya PWM (I)

- Hatua ya 16: Kuunda Moduli ya PWM- Funga Kazi ya PWM (II)

- Hatua ya 17: Kuunda Moduli ya PWM- Funga Kazi ya PWM (III)

- Hatua ya 18: Kuunda Moduli ya PWM- Ifanye Iendeshe

- Hatua ya 19: Utiririshaji wa Video kwenye Digilent ZYBO Na OV7670

- Hatua ya 20: Mchoro kamili wa Kuzuia

- Hatua ya 21: Unganisha OV7670 na ZYBO

- Hatua ya 22: Unda Kubuni Ubunifu

- Hatua ya 23: Ongeza faili za VHDL za Udhibiti na Kamata OV7670

- Hatua ya 24: Ongeza faili ya Vizuizi

- Hatua ya 25: Ongeza IP Repo kwa HLS IP

- Hatua ya 26: Ongeza Moduli na IP

- Hatua ya 27: Mipangilio ya Usanidi wa IP

- Hatua ya 28: Ongeza na usanidi kizuizi cha IP IP

- Hatua ya 29: Sehemu ya 1. Kuunda Moduli ya PWM kwa Servo Motors

- Hatua ya 30: Uunganisho wa Upande wa Kuingiza Video (aclk Imeangaziwa)

- Hatua ya 31: Uunganisho kwa OV7670

- Hatua ya 32: Uunganisho kwenye Upande wa Video

- Hatua ya 33: Run Run Automation na Connection

- Hatua ya 34: Tengeneza kifuniko cha HDL

- Hatua ya 35: Tengeneza Bitstream, Hamisha Vifaa kwa SDK, Fungua SDK Kutoka Vivado

- Hatua ya 36: SDK (hakuna FreeRTOS)

- Hatua ya 37: Utekelezaji wa FreeRTOS

- Hatua ya 38: Maagizo ya Matumizi

- Hatua ya 39: Marejeo na Viungo

- Mwandishi John Day day@howwhatproduce.com.

- Public 2024-01-30 12:54.

- Mwisho uliobadilishwa 2025-01-23 15:11.

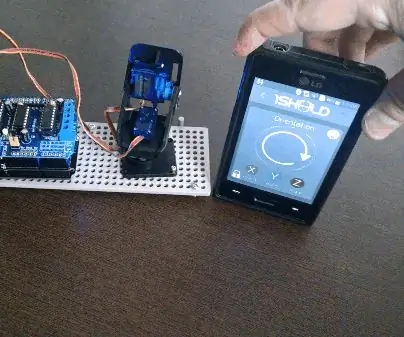

Anza kwa hatua ya kwanza kwa undani juu ya kuunda tu mtawala wa 2-axis servo PWM.

Anza kwenye mchoro mkubwa wa block (Hatua ya 19) kwa mradi kamili.

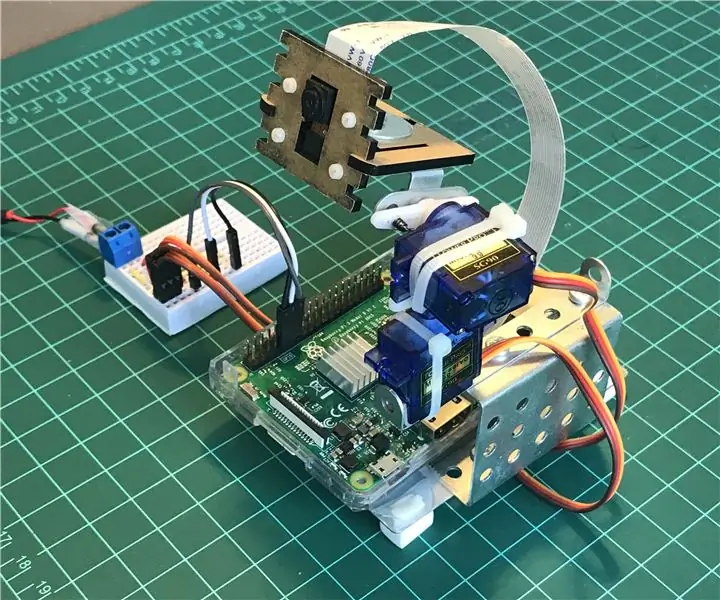

Kamera + Pan / usanidi wa tilt tuliyotumia:

PmodCON3 kutoka Digilent ilitumika kuunganisha servos.

Hatua ya 1: Kuunda Moduli ya PWM- Faili Chanzo

Hatua ya 2: Kuunda Moduli ya PWM- Usanidi wa Vivado

Kwanza, pakua Vivado Design Suite Kutoka kwa wavuti ya Xilinx. Sakinisha suti yote ya muundo, pamoja na Vivado Software Development Kit (SDK). Mradi huu unatumia toleo la 2017.2.

Wakati huo huo, Digilent Adept 2 inapaswa pia kusanikishwa kama dereva wa bodi ya Zybo.

Hatua ya 3: Kuunda Moduli ya PWM- Unda Faili ya Mradi

Kabla ya kuunda faili ya mradi, unapaswa kuhakikisha kuwa tayari umeweka faili ya Zybo vizuri kama mafunzo hapa:

Toleo la Vivado Toleo la 2015.1 na Ufungaji Baadaye wa Faili ya Bodi

Fungua Vivado 2017.2. Kwenye Anza haraka, bonyeza Bonyeza Mradi -> Ifuatayo -> Jina la Mradi (Taja jina la mradi wako hapa) -> Aina ya Mradi. Kwenye Aina ya Mradi, chagua Mradi wa RTL na uweke alama kwenye "Usitaje vyanzo wakati huu". Ifuatayo, kwa Sehemu ya Chaguo-msingi, chagua "Bodi" na "Zybo" kama Jina la Kuonyesha. Ifuatayo, Bonyeza Maliza kuanza mradi.

Hatua ya 4: Kuunda Moduli ya PWM- Kubuni Kubuni na Kuweka Picha Kizuizi (I)

Kwenye Navigator ya Mtiririko, bonyeza "" Unda Kubuni Kuzuia ", kisha bonyeza OK. bonyeza ishara "+" ili kuongeza IP muhimu. Ongeza:

- Mfumo mmoja wa Usindikaji wa ZYNQ7 mbili Timer AXI

- Kipima muda cha AXI mbili

Hatua ya 5: Kuunda Moduli ya PWM- Kubuni Kubuni na Kuweka Picha Kizuizi (II)

Baada ya Kuongeza IPs, Run Block Automation na automatisering ya uunganisho. Mara tu automatisering imekamilika, kwenye block "axi_timer_0", bonyeza kulia kwenye pwm0 -> Fanya ya nje. Taja pwm0 pini ya nje kama pwm_Xaxis. Pia, rudia mchakato hapo juu kwenye "axi_timer_1" na uipe jina pwm0 pini ya nje kama pwm_Zaxis.

Hatua ya 6: Kuunda Moduli ya PWM- Kubuni Ubunifu na Kuweka Picha Kizuizi (III)

Ona kwamba kila wakati tunapomaliza Kubuni ya Vitalu katika Vivado, tunahitaji kuunda Kifuniko cha HDL. Kwa kuwa itakuwa moduli ya kiwango cha juu kwa kila mradi.

Hatua ya 7: Kuunda Moduli ya PWM- Kubuni Ubunifu na Kuweka Picha Kizuizi (IV)

Sasa, tunahitaji kuanzisha faili yetu ya kikwazo kutoa pini zilizounganishwa na mchoro wetu wa kuzuia. Funga dirisha la Kubuni la Zuia, Kwenye kichupo cha Vyanzo, "Ongeza Vyanzo" -> Ongeza au unda vikwazo-> ongeza Zybo-Master.xdc kama faili zetu za kikwazo.

Hatua ya 8: Kuunda Moduli ya PWM- Kubuni Kubuni na Kuweka Picha Kizuizi (V)

Fungua faili ya kizuizi Zybo-Master.xdc kutoka folda ya Vizuizi, ondoa alama kwenye bandari ambazo tunataka kutaja kama ishara za pato na ubadilishe jina "get_ports {XXXX}", ambayo XXXX inaashiria pini ya nje iliyoitwa kwenye Mchoro wa Kizuizi. Mpangilio wa faili ya kikwazo unaonyeshwa kwenye takwimu.

Hatua ya 9: Kuunda Moduli ya PWM- Ufungaji wa vifaa

Unganisha motors za servo kwenye Pmod CON3. TowerPro SG90 ni mfano wa servo motor tuliotumia katika mradi huu. Kwa waya za servo, waya wa rangi ya machungwa inawakilisha ishara ya PWM, iliyounganishwa na pini ya SIG katika Pmod CON3. Waya nyekundu Vcc ni waya ya nguvu iliyounganishwa na pini ya VS katika Pmod CON3. Mwishowe, waya wa kahawia Gnd ni waya ya ardhini iliyounganishwa na pini ya GND. Ifuatayo, ingiza Pmod CON3 kwenye safu ya juu ya bandari ya JD kwenye Bodi ya Zybo.

Hatua ya 10: Kuunda Moduli ya PWM- Kuzalisha Bitstream na kuzindua SDK

1. Katika kichupo cha Navigator ya Mradi, endesha Tengeneza BitStream.

2. Hamisha vifaa: Faili> Hamisha> Hamisha vifaa -> alama kwenye "ni pamoja na mkondo mdogo" -> Sawa 3. Zindua SDK: Faili -> Zindua SDK.

Hatua ya 11: Kuunda Moduli ya PWM- Unda Programu mpya katika Xilinx SDK

Unda programu mpya:

Faili> Mpya> Mradi wa Maombi -> Ingiza jina la mradi wako -> Maliza

Chini ya Mradi wa Kugundua, lazima kuwe na folda tatu.

Katika kesi hii, "design_1_wrapper_hw_platform_0" ni folda iliyosafirishwa hapo awali na Vivado. Axis_2_PWM_SDK_bsp ni folda ya kifurushi cha msaada wa bodi. Na Axis_2_PWM_SDK ndio folda yetu kuu ya mradi katika SDK. Unaweza kuona faili ya "helloworld.c" chini ya folda ya "src" ya Axis_2_PWM_SDK, ambapo "helloworld.c" ni faili kuu.

Hatua ya 12: Kuunda Moduli ya PWM- Muhtasari wa Mradi wa Kugundua (I)

Wacha tuangalie faili zingine chini ya Mradi wa Kugundua. Kwanza, kwenye folda "design_1_wrapper_hw_platform_0", fungua "system.hdf". Faili hii inaonyesha ramani ya anwani ya processor ps7_cortex9 na vizuizi vya IP viko katika muundo wetu.

Hatua ya 13: Kuunda Moduli ya PWM- Muhtasari wa Mradi wa Kugundua (II)

Kisha, angalia faili ya "jumuisha" na "libsrc" chini ya folda ya "Axis_2_PWM_SDK_bsp". Faili za maktaba hapa zinatuwezesha kuingiliana na vifaa vya pembeni vya vifaa bila rejista za "kucheza".

Hatua ya 14: Kuunda Moduli ya PWM- Muhtasari wa Mtafiti wa Mradi (III)

Kupitia nyaraka za BSP, xtmrctr.h inapatikana kama Maktaba ya Kudhibiti Timer ya Xilinx inayohusiana na AXI Timer. Kwa kawaida, tunaweza kupata kazi inayotaka ya PWM hapa. Walakini, ukisoma nyaraka "tmrctr_v4_3", inaonyesha kuwa dereva kwa sasa haunga mkono utendaji wa PWM wa kifaa. Kwa sababu ya upungufu katika kazi ya PWM, lazima tufunge kazi yetu ya PWM kwa msaada wa xtmrctr.h na AXI Timer v2.0 LogiCORE IP Product Guide.

Hatua ya 15: Kuunda Moduli ya PWM- Funga Kazi ya PWM (I)

Rudi kwenye faili kuu "helloworld.c", pamoja na faili zifuatazo za kichwa:

Hatua ya 16: Kuunda Moduli ya PWM- Funga Kazi ya PWM (II)

Fafanua anwani za msingi za AXI TImer mbili kupitia "xparameters.h".

Hatua ya 17: Kuunda Moduli ya PWM- Funga Kazi ya PWM (III)

Jenga kazi inayotaka ya PWM.

Duty_val: hubadilisha thamani ya digrii kuwa mzunguko wa ushuru. PWM_Freq_Duty: weka mzunguko unaotakiwa na mzunguko wa ushuru ili kuzalisha PWM. Kipindi cha saa pia kinapaswa kupewa.

PWM_START: mpe anwani ya kujiandikisha ya PWM na uanze kutengeneza PWM.

PWM_STOP: toa anwani ya rejista ya PWM na uache kutengeneza PWM.

Nambari zingine za onyesho zinaonyeshwa kwenye "helloworld.c" chini ya "Axis_2_PWM_SDK"

Hatua ya 18: Kuunda Moduli ya PWM- Ifanye Iendeshe

1. Panga FPGA kupitia SDK

- Unganisha Bodi ya Zybo kupitia bandari ya USB kwa PC.

- Zana za Xilinx -> Programu ya FPGA

2. Endesha programu

Bonyeza ikoni ya "Run" na uangushe menyu -> Run As -> Anzisha kwenye Hardware

3. Kituo cha SDK

- Fungua Kituo cha SDK -> Unganisha kwa Bandari ya Serial -> Sawa

- Endesha programu. Ikiwa nambari ya onyesho inaendesha kwa mafanikio, unapaswa kuona "Uanzishaji umefanywa!" kwenye Kituo cha SDK.

Hatua ya 19: Utiririshaji wa Video kwenye Digilent ZYBO Na OV7670

Kamilisha faili ya kumbukumbu.

Hatua ya 20: Mchoro kamili wa Kuzuia

Hii inaonyesha mchoro kamili wa viunganisho vyote na vizuizi vya IP katika mradi huo

Hatua ya 21: Unganisha OV7670 na ZYBO

Unda unganisho kwa waya moduli ya ov7670 kwenye ZYBO Pmods

Takwimu Pmod ni Pmod D

Kudhibiti Pmod ni Pmod C

Kwa kuongeza, unganisha PmodCON3 na servos kama ilivyoainishwa katika nusu ya kwanza ya mafunzo haya

Hatua ya 22: Unda Kubuni Ubunifu

Katika Navigator ya Mtiririko, bonyeza "Unda muundo wa Kuzuia", kisha bonyeza OK.

Hatua ya 23: Ongeza faili za VHDL za Udhibiti na Kamata OV7670

Ongeza faili za VHDL zilizounganishwa na hatua hii kwenye mradi

Hatua ya 24: Ongeza faili ya Vizuizi

Ongeza faili ya vizuizi kwenye mradi wako.

Hatua ya 25: Ongeza IP Repo kwa HLS IP

Chukua faili ya Zip iliyoambatishwa na uifungue kwenye folda mpya iliyoitwa vile vile kwenye saraka mpya (folda) inayoitwa "HLS_repo".

Ongeza hazina ya IP kwenye mradi wako kwa kwenda kwenye orodha ya IP na bonyeza-kulia ukichagua "Ongeza Hifadhi …"

Nenda kwenye saraka yako ya "HLS_repo" na uchague.

Hiari: Unda mwenyewe usindikaji wa video ya HLS!

Hatua ya 26: Ongeza Moduli na IP

Ongeza moduli ya ov7670_axi_stream_capture, debute na ov7670_controller kwenye mchoro wa block kwa kubonyeza kulia nyuma na kuchagua "Ongeza Moduli…"

Vivyo hivyo, ongeza IPs:

- HLS_Video_Track

- Muundo wa Bafa ya Video Andika

- Soma Bafa ya Video Soma

- Kidhibiti cha Majira ya Video

- Mtiririko wa AXI4 kwa Video nje

- 3 ya "kipande"

- Mara kwa mara

- 2 ya kipima muda cha AXI

Hatua ya 27: Mipangilio ya Usanidi wa IP

Kama inavyoonyeshwa kwenye picha

Hatua ya 28: Ongeza na usanidi kizuizi cha IP IP

Ongeza Mfumo wa Usindikaji wa ZYNQ7 kwenye mchoro wa kuzuia

hariri usanidi:

-

Usanidi wa PS-PL

-

HP

- Washa S HP 0

- Washa S HP 1

-

- Usanidi wa saa

-

Saa za kitambaa za PL

- FCLK_0 kwa 100MHz

- FCLK_1 saa 25MHz (OutputClock)

- FLCK_2 saa 35MHz (<= 50MHz) (CameraClock)

-

Hatua ya 29: Sehemu ya 1. Kuunda Moduli ya PWM kwa Servo Motors

Toa axi_timer_0 pwm0 kwenye bandari mpya ya pwm_Xaxis

Toa axi_timer_1 pwm0 kwenye bandari mpya ya pwm_Zaxis

Hatua ya 30: Uunganisho wa Upande wa Kuingiza Video (aclk Imeangaziwa)

Unganisha sehemu za kuingiza video za IP kwa usahihi

(* uhusiano huu unapaswa kuundwa kwa kuchagua chaguo sahihi wakati wa kiotomatiki cha unganisho) "aclk" kutoka kwa axi_stream_capture huenda kwa:

- ap_clk kwenye bafa ya fremu ya video andika

- ap_clk kwenye kizuizi cha usindikaji wa mkondo wa video wa HLS

- * aclk kwenye AXI smartconnect IP kutoka kwa Baa ya Fremu ya Video Andika kwa S_AXI_HP0

- * aclk inayolingana na vituo vya IP ya AXI Interconnect ya vituo vya S_AXI vya kizuizi cha usindikaji wa video ya HLS na bafa ya fremu ya video andika S_AXI_HP0_ACLK kwenye kizuizi cha PS

Ishara ya mkondo wa video imeunganishwa tu katika safu kutoka kwa kizuizi cha kukamata hadi kiolesura cha kumbukumbu cha Zynq.

- Video huenda kutoka kwa kizuizi cha kukamata hadi kizuizi cha usindikaji cha HLS.

- Video iliyosindikwa kutoka kwa kizuizi cha HLS huenda kwenye kizuizi cha kuandika bafa ya fremu.

- * Kitufe cha kuandika bafa ya fremu kinaunganisha na kiunga cha HP0 kwenye kizuizi cha Zynq PS.

- Ishara ya m_axis_tuser kutoka kwa pato la kizuizi cha kukamata imeunganishwa kwa mikono kwa ishara ya kuingiza video_in_TUSER kwenye kizuizi cha usindikaji cha HLS na ishara ya ap_start kwenye kizuizi kimoja.

Ishara ya TUSER (tuser) hutumiwa na itifaki ya mkondo wa video ya AXI kuonyesha mwanzo wa sura ya video. AP_Start inaambia kizuizi cha HLS kuanza usindikaji. Wakati wa kuunganisha ishara moja ya basi na kuigawanya kwa mtindo huu ni muhimu pia kuiunganisha hatua ya kawaida ya kukomesha basi iliyobaki. Vivado inadhani kwamba ikiwa unaunganisha ishara hiyo kwa mikono kwamba unataka kukatiza kile ambacho kingeunganisha kawaida.

Mipangilio ya usanidi wa vizuizi vya IP:

Bafa ya fremu ya video andika:

Muundo wa video: RGB8

Sampuli 1 kwa saa Nguzo za Max: 1280 (> = 640) Safu za juu: 960 (> = 480) Upana wa data ya juu: 8

Hatua ya 31: Uunganisho kwa OV7670

Kwenye block block ya ov7670_axi_stream_capture

- Fanya pembejeo zote nje (bonyeza kulia kwenye pini na uchague kutoka kwenye menyu, au bonyeza kushoto-> ctrl + T)

- Acha majina jinsi yalivyo

Kwenye kizuizi cha mdhibiti wa ov7670_

- Fanya matokeo yote ya kuzuia nje

- Badili jina bandari iliyokamilishwa kuwa led0

- unganisha clk kwenye CameraClock (<= 50MHz) (FCLK_2)

Kwenye kizuizi cha kuondoa

- unganisha kitufe cha kifungo1 kwenye bandari ya pembejeo ya nje inayoitwa btn0

- unganisha nje1 kwa laini ya kutuma tena kwenye kizuizi cha IP cha ov7670_dhibiti

- unganisha kitufe cha kifungo2 kwenye bandari ya pembejeo ya nje inayoitwa btn3

- unganisha out2n kwa pembejeo ya ext_reset_in kwenye Mfumo wa processor wa Kuweka upya IP kwa kikoa cha saa ya kukamata video. (* Hii inaweza kuhitaji kufanywa baada ya IP hiyo kuzalishwa *)

- unganisha clk kwenye CameraClock (<= 50MHz) (FCLK_2)

Hatua ya 32: Uunganisho kwenye Upande wa Video

Uunganisho wa vizuizi vya Kidhibiti Saa cha Video (VTC), AXI4-Mkondo wa Video nje, na vipande

- Tumia saa 25MHz (FCLK_1) kwa vid_io_out_clk na clk ya VTC

- Tumia saa 100MHz (FCLK_0) kwa aclk kwenye AXI4-Mkondo ili Video Out

- kupimia_kuhusu vtiming_in

- Sura ya Video Soma m_axis_video huenda kwa AXI4-Mkondo wa Video Out video_in

- vtg_ce huenda kwa gen_clken

- Funga VTC clken, aclken, vid_io_out_ce kwa Constant dout [0: 0]

- Leta vid_hsync na vid_vsync nje kwa bandari za pato za nje vga_hs na vga_vs, mtawaliwa. (hayupo pichani)

Vipande:

- Vipande vinapaswa kusanidiwa kama inavyoonyeshwa kwenye picha zilizoambatishwa

- badilisha vizuizi kwa kipande-nyekundu, kipande-kijani, na kipande_bluu

- safu ya kuanzisha kama inavyoonyeshwa kwenye picha kwa jina la block

- unganisha kila pato la kipande kwenye pato la nje la bandari kama inavyoonekana kwenye picha.

- vid_data [23: 0] inaunganisha na pembejeo kwa kila kipande (Din [23: 0])

Hatua ya 33: Run Run Automation na Connection

Run Run Automation kuunganisha vitu kutoka kwa ZYNQ7 PS block. Kama inavyoonyeshwa na picha.

Endesha kiunganishi cha Uunganisho kuunda IP yote ya unganisho. Zingatia sana chaguzi zote kwenye kila picha.

Kwenye kizuizi cha kujiondoa, unganisha nje2n kwenye kikoa cha saa ya kukamata video Kichakata Mfumo wa Kuweka upya pembejeo ya ext_reset_in.

Hatua ya 34: Tengeneza kifuniko cha HDL

Tengeneza kifuniko cha HDL kwa muundo wako wa block.

Weka kama moduli ya juu.

Hatua ya 35: Tengeneza Bitstream, Hamisha Vifaa kwa SDK, Fungua SDK Kutoka Vivado

Hakikisha kuingiza mkondo kidogo katika usafirishaji.

Kizazi cha mkondo mdogo kinaweza kuchukua muda mrefu sana.

Kisha uzindua SDK

Hatua ya 36: SDK (hakuna FreeRTOS)

Toleo hili hufanya kila kitu bila kutumia FreeRTOS, ikibadilisha nambari vizuri.

Unda BSP ya pekee kulingana na muundo wa vifaa. Chaguo chaguomsingi zinapaswa kuwa sawa. Hakikisha vyanzo vya BSP vimetengenezwa.

Unda Programu kama inavyoonyeshwa kwenye Picha. (programu tupu)

Futa kuu iliyozalishwa kiotomatiki na uingize faili zilizoambatishwa.

Hatua ya 37: Utekelezaji wa FreeRTOS

Toleo hili linatumia FreeRTOS. Crere FreeRTOS901 BSP kulingana na muundo wa vifaa. Chaguo chaguomsingi zinapaswa kuwa sawa. Hakikisha vyanzo vya BSP vimetengenezwa.

Unda Programu kama inavyoonyeshwa kwenye Picha. (programu tupu)

Futa kuu iliyozalishwa kiotomatiki na uingize faili zilizoambatishwa.

Hatua ya 38: Maagizo ya Matumizi

Mradi huu ni ngumu sana kuendeshwa. Fuata hatua kwa utaratibu.

Hakikisha kwamba ZYBO yako haipakia chochote wakati inapowashwa. Hii inamaanisha kuwa Done ya Done haipaswi kuwasha. Njia moja ya kufanya hivyo ni kuweka jumper ya chanzo cha boot kwa JTAG.

Fungua mradi (FreeRTOS au la) unayotaka kupanga kutoka SDK

- Washa ZYBO yako. LED iliyofanywa haipaswi kuwaka.

- Panga FPGA na faili kidogo. LED iliyofanywa inapaswa kuangaza. Led0 haipaswi kuwaka.

- Tumia nambari hiyo (kumbuka kupita mahali pa kuanza ikiwa unafanya hivyo).

Kwa wakati huu unapaswa kupata pato kwenye onyesho lako la VGA.

Kuanzisha upya (ikiwa ni mende au chochote): gonga haraka kitufe cha PS-SRST au uzime ZYBO kisha urudi. Endelea kutoka hatua ya 2.

Kusimamisha processor na kitatuaji itasababisha Kamera kushikilia msimamo badala ya kusonga. Mtiririko wa video utaendelea hata hivyo.

Hatua ya 39: Marejeo na Viungo

Miongozo ya kumbukumbu ya Xilinx na nyaraka:

- PG044 - Mtiririko wa AXI kwa Video nje

- PG278 - Bafa ya Fremu ya Video Soma / Andika

Viungo vingine:

- Blogi ya Lauri - pembejeo ya VDMA

- Blogi ya Lauri - OV7670 kwa pato la VGA kwa kutumia BRAM

- Hamsterworks wiki, na Mike Fields, chanzo asili cha nambari ya OV7670

- Hati ya data inayoonyesha vipimo vya msingi vya muda

Ilipendekeza:

Udhibiti wa Blinds na ESP8266, Nyumba ya Google na Ushirikiano wa Openhab na Udhibiti wa Wavuti: Hatua 5 (na Picha)

Udhibiti wa Blinds na ESP8266, Nyumba ya Google na Ushirikiano wa Openhab na Udhibiti wa Wavuti: Katika hii Inayoweza kufundishwa ninakuonyesha jinsi nilivyoongeza kiotomatiki kwa vipofu vyangu. Nilitaka kuweza kuiongeza na kuiondoa kiotomatiki, kwa hivyo usanikishaji wote ni sehemu ya. Sehemu kuu ni: Stepper motor Stepper driver inadhibitiwa bij ESP-01 Gear na kuweka

Pan Tilt Inadhibitiwa na Simu ya Mkondoni: Hatua 4

Pan Tilt Inadhibitiwa na Simu ya rununu: Halo wote, Katika mradi wangu huu mpya nitakuletea Pan-Tilt inayodhibitiwa na Simu ya rununu. Mwendo wote wa simu ya rununu umezalishwa tena kwenye kifaa cha kugeuza pan kupitia Bluetooth. Ujenzi ni mzuri sana. rahisi kutumia Arduino R3 (au sawa) na tw

Pan na Tilt Mechanism ya DSLR Muda Kupita: Hatua 7 (na Picha)

Pan na Tilt Mechanism ya DSLR Muda Uliopita: Nilikuwa na motors chache za stepper zilizokuwa zimezunguka na nilitaka kuzitumia kutengeneza kitu kizuri. Niliamua kuwa nitatengeneza mfumo wa Pan na Tilt kwa kamera yangu ya DSLR ili nipate kuunda wakati mzuri. Vitu utahitaji: 2x stepper motors -htt

IOT123 - SOLAR TRACKER - TILT / PAN, fremu ya Paneli, LDR MOUNTS RIG: Hatua 9 (na Picha)

IOT123 - SOLAR TRACKER - TILT / PAN, fremu ya Paneli, LDR MOUNTS RIG: Mengi ya miundo ya DIY ya wafuatiliaji wa jua wa mhimili mbili " huko nje " ni msingi wa 9G Micro Servo ambayo imepimwa kwa kiwango cha chini kuzunguka Seli kadhaa za jua, mdhibiti mdogo, betri na nyumba. Unaweza kubuni karibu

Pan-Tilt Multi Servo Control: Hatua 11 (na Picha)

Pan-Tilt Multi Servo Control: Kwenye mafunzo haya, tutachunguza jinsi ya kudhibiti servos nyingi kwa kutumia Python kwenye Raspberry Pi. Lengo letu litakuwa utaratibu wa PAN / TILT kuweka kamera (PiCam) Hapa unaweza kuona jinsi mradi wetu wa mwisho utakavyofanya kazi: Dhibiti mtihani wa kitanzi cha Udhibiti wa Servo: