Orodha ya maudhui:

- Mwandishi John Day [email protected].

- Public 2024-01-30 12:48.

- Mwisho uliobadilishwa 2025-01-23 15:11.

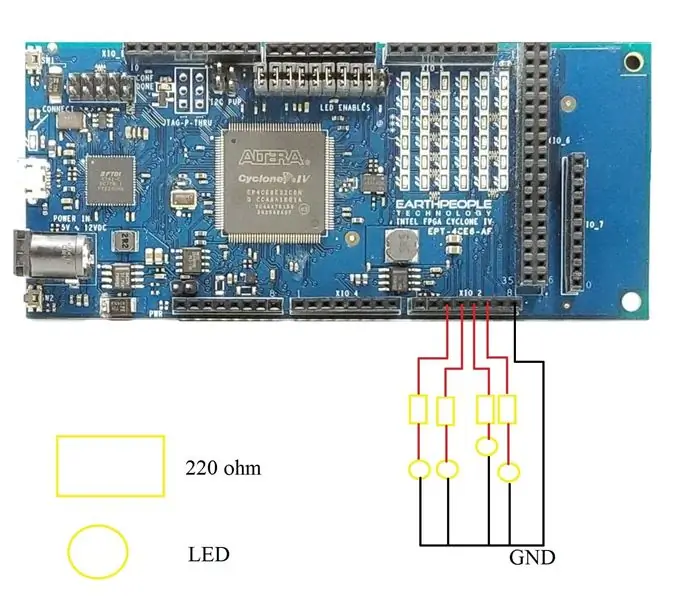

Katika mafunzo haya, tutatumia FPGA kudhibiti mzunguko wa nje wa LED. Tutafanya kazi zifuatazo

(A) Tumia vifungo vya kushinikiza kwenye FPGA Kimbunga IV DuePrologic kudhibiti LED.

(B) Taa ya kuwasha na kuzima mara kwa mara

Demo ya video

Menyu ya Maabara:

Hatua ya 1: Jenga Mzunguko wa Elektroniki

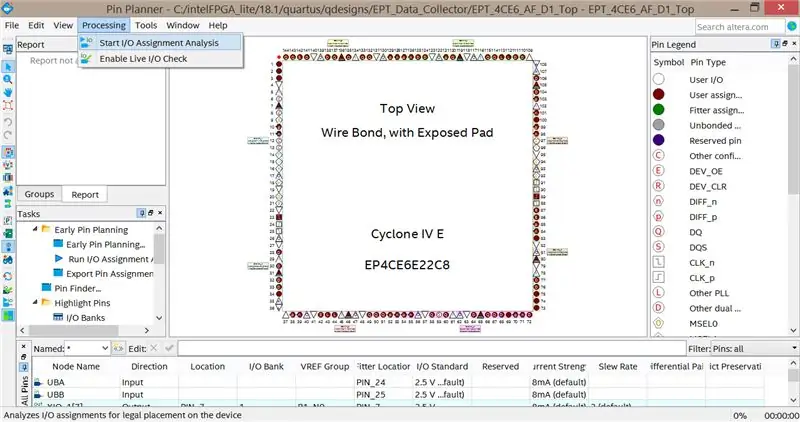

Hatua ya 2: Angalia Mpangaji wa Pin na Hariri Nambari ya Verilog

Hatua ya 3: Hariri Nambari ya Verilog

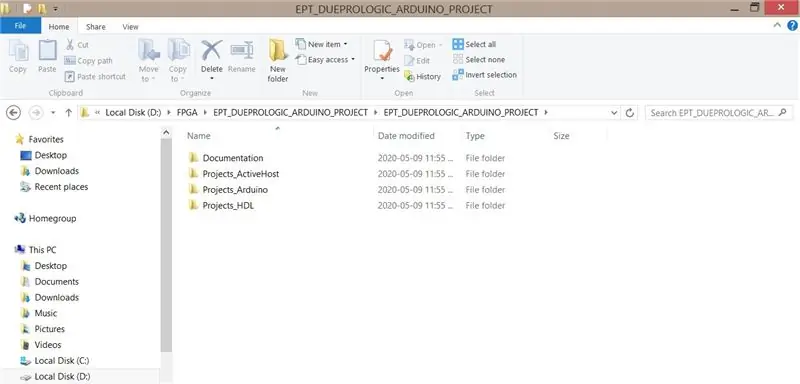

Unaponunua FPGA DueProLogic, unapaswa kupokea DVD. Baada ya kufungua "Projects_HDL", unapaswa kuona faili asili ya nambari

Ongeza nambari iliyoangaziwa. Inasajili bandari za I / O na kutoa nambari kwa bandari.

waya wa pato [7: 0] XIO_1, // XIO - D2-D9

waya wa pato [5: 0] XIO_2, // XIO - D10-D12

waya wa pato [5: 0] XIO_3, // XIO - D22-D29

waya wa kuingiza [5: 0] XIO_4, // XIO - D30-D37

waya wa kuingiza [5: 0] XIO_5, // XIO - D38-D45

waya wa pato [4: 0] XIO_6_OUT, // XIO - D46-D53

waya wa kuingiza [31: 5] XIO_6, // XIO - D46-D53

waya wa pato [2: 0] XIO_7, // XIO - D69, D70, D71, D74, D75, D76

waya wa pembejeo UBA, // Kitufe cha Bonyeza

waya wa pembejeo UBB // Kitufe cha Kushinikiza

pea XIO_1 [3] = start_stop_cntrl;

pea XIO_2 [1] = start_blinky; // LED flash LED juu na mbali

mpe XIO_2 [2] = 1'b1; // pato la juu

pea XIO_2 [3] = ~ UBA; // Kitufe cha kushinikiza A

pea XIO_2 [4] = UBB; // Kitufe cha kushinikiza B

pea c_enable = XIO_5 [2];

mpe LEDExt = XIO_5 [5];

Kisha lazima tuweke muda wa kuchelewesha. Toa maoni nambari ya awali ya saa na uandike kazi mpya ya kipima muda

//-----------------------------------------------

// LED Blinky kuanza

//-----------------------------------------------

/*

daima @ (posedge CLK_66 au negedge RST)

anza

ikiwa (! RST)

Anza_blinky <= 1'b0;

mwingine

anza

ikiwa (daftari_sajili [7: 4]> 0)

Anza_blinky <= 1'b1;

mwingine

Anza_blinky <= 1'b0;

mwisho

mwisho

*/

reg [31: 0] zamani;

mwanzo kuanza

ex <= 32'b0;

Anza_blinky <= 1'b0;

mwisho

daima @ (posedge CLK_66)

anza

ex <= ex + 1'b1;

ikiwa (ex> 100000000) // flash on / off ~ sekunde 1.6, saa 66MHz

anza

Anza_blinky <=! Anza_blinky;

ex <= 32'b0;

mwisho

mwisho

//-----------------------------------------------

// Taa ya Kuchelewesha Timer ya LED

//-----------------------------------------------

/*

daima @ (posedge CLK_66 au negedge RST)

anza

ikiwa (! RST)

kuongozwa_kucheleweshwa_kuhesabu <= TIMER_LOW_LIMIT;

mwingine

anza

ikiwa (sema [SELECT_MODE])

kuongozwa_kucheleweshwa_kuhesabu <= timer_thamani;

vinginevyo ikiwa (sema [WAIT_FOR_TIMER])

kuongozwa_kucheleweshwa_kuhesabu <= kuongozwa_kucheleweshwa_kuhesabu - 1'd1;

mwisho

mwisho * /

Hatua ya 4: Tunga Nambari ya Verilog

Bonyeza "Anzisha Mkusanyiko" huko Quartus, hakuna ujumbe wowote wa makosa unapaswa kuzalishwa.

Ukipokea ujumbe wa makosa juu ya pini nyingi. Nenda kwenye Kazi -> Kifaa -> Chaguzi za Kifaa na Pini -> Pini za Kusudi-Dual -> badilisha thamani ya pini inayofaa kuwa "Tumia kama I / O ya kawaida".

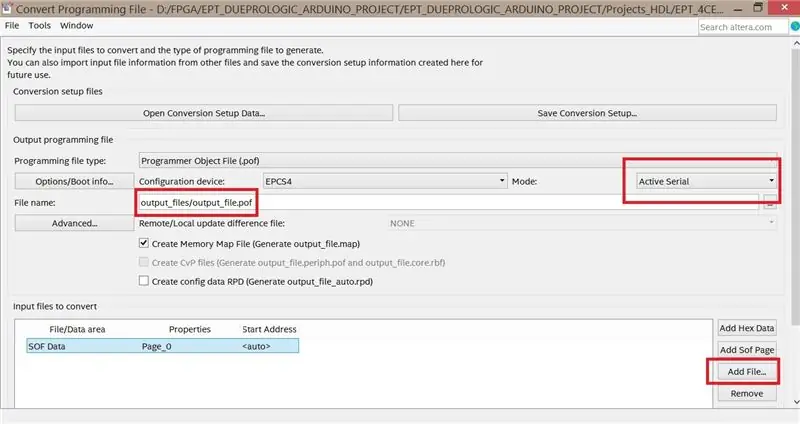

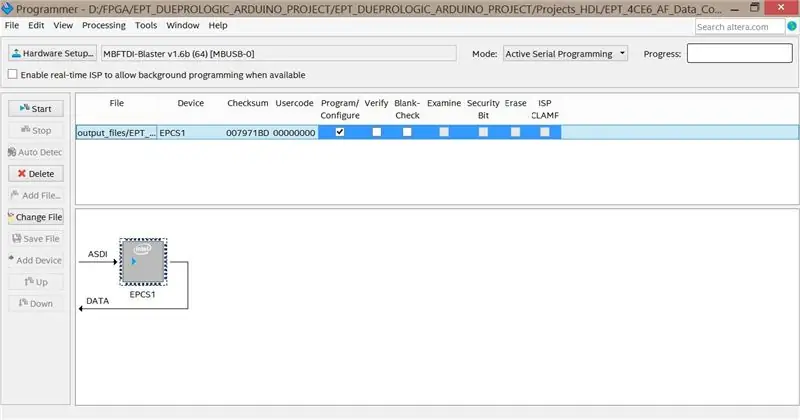

Baada ya mkusanyiko, unapaswa kupata faili ya pof pato moja kwa moja. Ikiwa programu yako haijasasishwa, unaweza kupata faili laini tu. Inapotokea, bonyeza "Faili" katika Quartus -> "badilisha faili za programu". Badilisha mipangilio ambayo imewekwa alama na masanduku nyekundu.

Hatua ya 5: Wacha tuijaribu

Baada ya yote, inapaswa kufanya kazi !!! LED ya manjano inawashwa kila wakati. LED nyekundu inaangaza. LED ya bluu imezimwa ikiwa bonyeza kitufe B. LED ya kijani imewashwa ikiwa bonyeza kitufe cha A

Ilipendekeza:

FPGA Kimbunga IV Kutokana na Udhibiti wa ProLogic Kamera ya Raspberry Pi: Hatua 5

FPGA Kimbunga IV Kutokana na Udhibiti wa Kamera ya Raspberry Pi: Licha ya FPGA DueProLogic imeundwa rasmi kwa Arduino, tutafanya FPGA na Raspberry Pi 4B kuambukizwa. Kazi tatu zinatekelezwa katika mafunzo haya: (A) Wakati huo huo bonyeza vifungo viwili vya kushinikiza FPGA kubatilisha pembe ya

FPGA Kimbunga IV KutokanaProLogic Udhibiti Servo Motor: 4 Hatua

FPGA Kimbunga IV Kutokana na Udhibiti wa Servo Motor: Katika mafunzo haya, tutaandika nambari ya Verilog kudhibiti servo motor. Servo SG-90 imetengenezwa na Waveshare. Unaponunua servo motor, unaweza kupokea data ambayo inaorodhesha voltage ya uendeshaji, muda wa juu na Pu inayopendekezwa

AccuRep: Kifaa cha Kuhesabu cha kushinikiza: Hatua 8 (na Picha)

AccuRep: Kifaa cha Kuhesabu cha kushinikiza: Najua watu wengi ambao wameanza kufanya kazi ya karantini hii. Shida ya mazoezi ya nyumbani ni ukosefu wa vifaa vya mazoezi. Mazoezi yangu yana vyenye kushinikiza. Ili kujisukuma sana, nasikiliza muziki wa rock wakati wa mazoezi yangu. Shida ni hesabu ya rep.

O Mfano wa Reli Kimbunga Kimbunga: Hatua 16

O Aina ya Reli ya Kimbunga Kimbunga: Nina hakika kila mtu ameona Kimbunga kwenye video. Lakini umeona moja ikifanya kazi kwa uhuishaji kamili kwenye O Scale Model Railroad? Kweli hatuna bado imewekwa kwenye reli, kwa sababu ni sehemu ya mfumo kamili wa sauti na uhuishaji.

Kimbunga cha LED Arcade Mchezo: 4 Hatua

Kimbunga cha Arcade Game: Kusudi la mradi huu ilikuwa kuunda mchezo rahisi kwa kutumia Arduino ambayo ingekuwa inaingiliana na burudani kwa watoto. Nakumbuka mchezo wa Arcade wa Kimbunga ukiwa moja ya michezo ninayopenda sana wakati nilikuwa mdogo, kwa hivyo niliamua kuiga tena. T