Orodha ya maudhui:

- Hatua ya 1: Zuia Mchoro

- Hatua ya 2: Kanuni ya Uendeshaji

- Hatua ya 3: Utekelezaji wa Mantiki

- Hatua ya 4: Kutatua vikwazo

- Hatua ya 5: Usanidi wa Kifaa - Mzunguko wa Matrix0

- Hatua ya 6: Usanidi wa Kifaa - Mantiki ya Kufunga ya SPI

- Hatua ya 7: Usanidi wa Kifaa - Sifa za Vipengele vya Matrix0

- Hatua ya 8: Usanidi wa Kifaa - Mzunguko wa Matrix1

- Hatua ya 9: Usanidi wa Kifaa - Kaunta ya Kibinadamu ya 3-bit

- Hatua ya 10: Usanidi wa Kifaa - 3-bit Linganisha Logic

- Hatua ya 11: Usanidi wa Kifaa - Mlinganisho wa Dijitali na Usajili wa Muda

- Hatua ya 12: Usanidi wa Kifaa - Sifa za Vipengele vya Matrix1

- Hatua ya 13: Matokeo

- Mwandishi John Day day@howwhatproduce.com.

- Public 2024-01-30 12:50.

- Mwisho uliobadilishwa 2025-01-23 15:11.

Mifumo ya kudhibiti na vifaa vinavyohusiana vinahusika na vyanzo vingi vya nguvu, kama vile mistari ya upendeleo au betri, na lazima ifuate laini ya juu zaidi (au ya chini kabisa) kati ya seti fulani.

Kwa mfano, ubadilishaji wa mzigo katika mfumo wa nguvu wa "betri nyingi" unahitaji kwamba mfumo unafuatilia kiwango cha chini au kiwango cha juu cha voltage kati ya safu ya betri (kiwango cha juu au min kama kazi ya algorithm fulani ya kubadili) na kwa nguvu hubadilisha mzigo kwenda chanzo sahihi zaidi kwa wakati halisi. Vinginevyo, mfumo unaweza kuhitaji kuunganisha kwa muda betri ya chini kabisa kwa kuchaji sahihi.

Mfano mwingine ni mfumo wa kisasa wa umeme wa jua, ambapo kila jopo la jua lina vifaa vya utaratibu wa tiltrotate na mzunguko wa ufuatiliaji wa jua (mwisho huu unatoa habari ya nafasi ya Jua kuelekeza jopo). Pamoja na maelezo ya max-voltage, kila nafasi ya jopo la jua inaweza kupangwa vizuri kwa msingi wa jopo la kamba inayotoa voltage ya pato kubwa zaidi, na hivyo kufikia kiwango bora cha utumiaji wa nguvu.

Kuna bidhaa kadhaa tofauti za IC za kibiashara (haswa watawala wadogo) ambazo kwa kanuni zinaweza kutekeleza mfuasi wa kiwango cha juu. Walakini, zinahitaji programu na hazina gharama nafuu kuliko suluhisho la ishara-mchanganyiko. Kuongezea muundo wa Mazungumzo ya GreenPAK ™ kunaweza kuathiri upatikanaji, ukubwa, na muundo wa muundo. Ubunifu huu hutumia faida ya kujumuisha mzunguko wa analog na dijiti kwenye chip moja moja.

Katika Agizo hili, mwisho wa mbele wa analog na mantiki ya dijiti inahitajika kutekeleza upataji wa voltage ya juu (au mwishowe min) kati ya vyanzo nane tofauti hutekelezwa.

Kutekeleza ufuatiliaji wa voltage ya njia-8 ya analox / min voltage SLG46620G hutumiwa.

Hapo chini tulielezea hatua zinazohitajika kuelewa jinsi suluhisho limepangiliwa kuunda njia-8 za analog max / min voltage monitor. Walakini, ikiwa unataka tu kupata matokeo ya programu, pakua programu ya GreenPAK ili kuona Faili ya Ubunifu wa GreenPAK iliyokamilishwa tayari. Chomeka Kitengo cha Maendeleo cha GreenPAK kwenye kompyuta yako na hit program ili kuunda mfuatano wa njia 8 za analog max / min voltage.

Hatua ya 1: Zuia Mchoro

Kielelezo 1 kinaonyesha mchoro wa ulimwengu wa mfumo uliotekelezwa.

Kamba ya hadi vyanzo 8 vya voltage anuwai imechanganywa na kuingiliana na moduli ya ADP ya GreenPAK iliyounganishwa na muundo wa ndani uliobinafsishwa unaoweza kuchagua chanzo na voltage ya juu zaidi kwa wengine. Mantiki ya ndani hutoa habari hii kwa onyesho au usindikaji zaidi.

Ubunifu huo unategemea bidhaa ya GreenPAK SLG46620G, kwa sababu inaambatisha vizuizi vyote muhimu vya ujenzi wa dijiti na dijiti kwa programu hiyo. Katika utekelezaji huu safu hiyo inachunguzwa kwa njia ya multiplexer ya analoji ya ADG508 inayoongozwa moja kwa moja na GreenPAK IC.

Habari ya pato ni nambari ya dijiti ya 3-bit inayolingana na nambari ya chanzo cha voltage katika voltage kubwa. Njia ya moja kwa moja ya kupata habari hii ni kuonyesha nambari kupitia onyesho la sehemu 7. Inaweza kutekelezwa kwa urahisi kwa kuingiliana na pato la dijiti la SLG46620G kwa dereva wa sehemu-7, kama suluhisho la GreenPAK ilivyoelezewa kwa Rejea au kwa 74LS47 IC ya kawaida.

Mzunguko uliowasilishwa unatafuta kiwango cha juu cha voltage. Kubadilisha muundo kuwa kipata cha chini cha voltage, mzunguko rahisi wa pre-conditioning lazima uongezwe kati ya multiplexer ya analog na pembejeo ya analog ya GreenPAK, ukitoa pato la multiplexer kutoka kwa voltage ya kumbukumbu ya 1 V.

Hatua ya 2: Kanuni ya Uendeshaji

Ubunifu unakusudia kuchagua chanzo na kiwango cha juu cha voltage, kwa hivyo skana hufanywa kwa safu nzima wakati wa kuhifadhi dhamana ya mwisho na kuilinganisha na thamani inayofuata katika pembejeo (ambayo ni ya chanzo cha voltage inayofuata katika skanning).

Katika yafuatayo tutarejelea mlolongo kamili wa kuzidisha pamoja na pembejeo zote kama "skanisho" au "kitanzi".

Kulinganisha kati ya maadili mawili hakutekelezwi kwa njia ya vifaa vya ACMP (hata hivyo, inapatikana katika SLG46620G), lakini badala ya moduli ya DCMP, mara tu maadili yatakapowekwa kwa dijiti. Hii ni mbinu ya hali ya juu na iliyosafishwa kwanza kushughulikiwa katika Rejea.

Kielelezo 2 kinaonyesha jinsi SLG46620G imeundwa kwa muundo huu.

Ishara ya pembejeo ya analogi huenda kwa pembejeo ya ADC kupitia sehemu ya PGA na Faida iliyowekwa ya 1. Mipangilio anuwai ya Faida pia inawezekana kupata mechi bora na vifaa vya elektroniki vya hali ya mbele vilivyojitolea kuchora voltages za pembejeo kwa 0-1 V anuwai ya moduli ya GreenPAK ADC.

ADC inafanya kazi kwa hali ya kumaliza moja na inabadilisha ishara ya analog kuwa nambari ya dijiti 8-bit, ambayo huhamishiwa kwenye moduli ya DCMP. Nambari ya dijiti pia imeingizwa kwenye kizuizi cha SPI, kimeundwa kama Bafa ya ADC / FSM, ambapo nambari ya dijiti inaweza kuhifadhiwa na haitabadilishwa hadi mapigo yajayo yaingie kwa uingizaji wa SPI CLK. Tambua kuwa kizuizi cha mantiki kinajitolea kuingiza SPI CLK. Tutachunguza sehemu hii baadaye, kwani hii ndiyo mantiki "ya msingi" inayohusika na utendaji mzuri. Nambari mpya ya dijiti imehifadhiwa kwenye moduli ya SPI ikiwa tu ni ya voltage halisi ya pembejeo.

Sehemu ya DCMP inatumiwa kulinganisha data ya sasa ya ADC na mshindi wa mwisho (hiyo ni max ya mwisho kupatikana) ambayo imehifadhiwa kwenye kizuizi cha SPI. Itatoa mapigo kwenye OUT + pato wakati data mpya ya ADC ni kubwa kuliko ile ya awali. Tunatumia ishara ya OUT + kusasisha kizuizi cha SPI na mshindi mpya.

Ishara ya saa ya ulimwengu inaendesha ubadilishaji wa ADC na nyakati za jumla. Mara tu ubadilishaji utakapofanywa, mapigo ya ishara ya pato ya ADC ya INT, iliyoratibiwa kwa wakati na pato la data linalofanana la ADC. Tunatumia pato la INT pia kuongeza kaunta ya biti-3-bit, inayotekelezwa na DFF katika Matrix1, ambayo ni muhimu kwa sababu tatu:

1. Mistari ya pato inakabiliana na multiplexer ya nje ya analog, na hivyo kutumikia voltage inayofuata ya pembejeo kwa ADC;

2. Hesabu imehifadhiwa kwenye rejista ya 3-bit (iliyotekelezwa katika Matrix1) kuhifadhi mshindi wa muda wakati wa skana;

Hesabu imesimbuliwa kusasisha rejista ya pili ya 3-bit (iliyotekelezwa katika Matrix0) mara tu skanisho imekamilika.

Hatua ya 3: Utekelezaji wa Mantiki

Moduli ya ADC mtiririko hutoa data iliyobadilishwa ya voltages zote za kuingiza, moja baada ya nyingine, kwa muda usiojulikana. Multiplexer ikishughulikiwa 0b111 (decimal 7), kaunta inaendelea hadi 0b000 (decimal 0) na hivyo kuanza skanning mpya ya voltages za kuingiza.

Wakati wa skana, ishara ya pato ya ADC INT inazalishwa wakati utaftaji wa data sawa ni halali. Wakati ishara hii inapiga, multiplexer ya analog inapaswa kubadili pembejeo inayofuata, ikitoa PGA na voltage inayofanana. Kwa hivyo, pato la ADC INT ni ishara ya moja kwa moja ya saa ya 3-bit Binary Counter ya Kielelezo 2, ambaye neno-pato linalofanana la 3-bit linashughulikia moja kwa moja multiplexer ya nje ya analog ("V chagua" kwenye Mchoro 1).

Wacha turejee mfano ambapo voltages za kuingiza zinatakiwa kuwa na uhusiano ufuatao:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

Kielelezo 3 kinawakilisha ishara kuu zinazohusika katika utaratibu wa uamuzi wa juu.

Kwa kuwa data hatimaye imewekwa kwenye rejista ya bafa ya SPI sawasawa na kunde za INT, dirisha la kulinganisha lipo ambapo yaliyomo bafa ya SPI inalinganishwa na matokeo ya uongofu ya ADC. Wakati huu husababishwa katika kizazi cha OUT + kunde kwenye pato la DCMP. Tunaweza kuchukua faida ya kunde hizi kupakia maadili mapya kwenye rejista ya bafa ya SPI.

Kama inavyoonekana kutoka kwa laini ya data ya bafa ya SPI ya Kielelezo kilichotangulia, rejista ya SPI daima ina, wakati kwa wakati, thamani kubwa kati ya pembejeo 8 na inasasishwa tu wakati dhamana kubwa hugunduliwa na moduli ya DCMP (ikimaanisha DCMP OUT + mstari wa pato la njama hiyo, kunde zinazokosekana husababisha V2 kubaki imewekwa kwenye rejista hadi ikilinganishwa na V5).

Hatua ya 4: Kutatua vikwazo

Ikiwa mantiki iliyotekelezwa ingekuwa kama ilivyoelezewa hapo juu, ni wazi kwamba tutaingia katika hali ya kutuliza: mfumo huo una uwezo wa kugundua voltages tu zilizo juu kuliko ile inayolingana na kile kilichohifadhiwa kwenye rejista ya bafa ya SPI.

Hii pia ni halali ikiwa voltage hii itapungua halafu pembejeo nyingine, hadi sasa iko chini kuliko hiyo, inakuwa ya juu zaidi: haiwezi kugunduliwa. Hali hii inaelezewa vizuri katika Mchoro 4 ambapo voltages 3 tu za pembejeo zipo kwa sababu ya uwazi.

Wakati wa iteration 2, matone ya V3 na V1 ndio voltage halisi ya juu. Lakini moduli ya DCMP haitoi pigo kwa sababu data iliyohifadhiwa kwenye rejista ya bafa ya SPI (inayolingana na 0.6 V) ni kubwa kuliko ile inayolingana na V1 (0.4 V).

Mfumo huo hufanya kama mpataji "kamili" na haisasishi pato kwa usahihi.

Njia nzuri ya kushinda shida hii ni kulazimisha kupakia tena data kwenye Rejista ya Bafa ya SPI wakati mfumo unakamilisha mzunguko kamili wa upigaji kura wa chaneli zote.

Kwa kweli, ikiwa voltage kwenye pembejeo hiyo bado ni kubwa zaidi, hakuna kinachobadilika na udhibiti unaendelea salama (ikimaanisha Kielelezo 4 hapo juu, hii ndio kesi ya Kitanzi cha Kitanzi 0 na 1). Kwa upande mwingine, ikiwa voltage kwenye pembejeo hiyo kwa bahati hupungua kwa thamani chini ya ingizo lingine, kisha kupakia tena thamani kunatoa uwezekano kwa moduli ya DCMP kutoa kipigo cha OUT + wakati ukilinganisha na thamani mpya ya max (hii ni kesi ya Kitanzi Ishara 2 na 3).

Kipande cha mzunguko wa mantiki ni muhimu kushinda shida. Lazima itoe ishara ya saa kwa sehemu ya SPI wakati kitanzi kinafikia pembejeo halisi, na hivyo kulazimisha kupakia tena neno lake la data iliyosasishwa kwenye Rejista ya Bafa ya SPI. Hii itajadiliwa katika Sehemu 7.2 na 7.6 hapa chini.

Hatua ya 5: Usanidi wa Kifaa - Mzunguko wa Matrix0

SLG46620G ina vizuizi viwili vya Matrix, kama ilivyoonyeshwa kwenye Kielelezo 2. Takwimu zifuatazo zinaonyesha usanidi wa vifaa husika.

Sehemu ya juu ya mzunguko ni "Rejista ya Kitanzi" inayopatikana na 3 DFFs (DFF0, DFF1, na DFF2). Inaburudishwa baada ya kila kitanzi cha multiplexer ya pembejeo kutuma kwa dereva wa sehemu-7 ya kuonyesha nambari ya binary ya "mshindi", ambayo ni pembejeo na voltage ya juu katika skanisho la mwisho. Saa zote kwa DFF na data hutoka kwa mantiki iliyotekelezwa kwa Matrix1 kupitia, mtawaliwa, bandari P12, P13, P14, na P15.

Sehemu ya chini ni mwisho wa mbele wa analog na pembejeo kwenye Pin 8 na PGA na faida x1. Pato la ADC INT huenda kwa mantiki ya saa ya SPI na kwa Matrix1 kupitia bandari P0, ambapo itatumika kama ishara ya saa kwa kaunta iliyotekelezwa.

Matokeo ya data ya ADC na SPI sambamba yameandikwa NET11 na NET15 kuunganishwa na sehemu ya DCMP katika Matrix1.

Hatua ya 6: Usanidi wa Kifaa - Mantiki ya Kufunga ya SPI

Kama ilivyoonyeshwa hapo awali katika sehemu ya "Utekelezaji wa Mantiki", Sajili ya Bafa ya SPI inasasishwa kila wakati kulinganisha kati ya thamani halisi iliyohifadhiwa na data mpya ya ubadilishaji wa ADC inazalisha mapigo kwenye pato la DCMP OUT +.

Uadilifu wa ishara unahakikishiwa ikiwa ishara hii ime-AND-ed na pato la ADC INT. Hii inepuka mwanya wowote na uchochezi wa uwongo.

Pia tumetilia mkazo kwamba kuruka hali ya kutokukamilika, bafa ya SPI lazima isasishwe wakati kitanzi kinafikia data halisi ya mshindi.

Ishara tatu basi ziko kwenye mchezo kwa saa sahihi ya SPI:

1. Pato la ADC INT (LUT0-IN1)

2. Pato la DCMP OUT + (LUT0-IN0 kupitia bandari P10)

3. Hesabu ni sawa na ishara ya Latch (LUT0-IN2 kupitia bandari P11)

Hizi mbili za kwanza zimepangwa-na zimeorodheshwa na zote mbili zimepangwa-na-za-mwisho na LUT0, ambayo utekelezaji wake umesanidiwa kama kwenye Mchoro wa 6.

Hatua ya 7: Usanidi wa Kifaa - Sifa za Vipengele vya Matrix0

Takwimu 7-10 zinaonyesha vifaa vilivyobaki windows windows mali ya Matrix0.

Hatua ya 8: Usanidi wa Kifaa - Mzunguko wa Matrix1

Hatua ya 9: Usanidi wa Kifaa - Kaunta ya Kibinadamu ya 3-bit

Sehemu ya juu ya mzunguko ina vitu vya mantiki, haswa kaunta ya biti 3-bit iliyowekwa na pato la ADC INT, kama ilivyojadiliwa tayari. Kaunta hii inatekelezwa kwa skimu ya "kiwango" iliyoonyeshwa kwenye Kielelezo 12.

Kaunta hii inatambulika katika muundo wetu kupitia Flip-Flops DFF9, DFF10, DFF11 na INV1, LUT4, LUT8. Pato la DFF9 ni LSB wakati DFF11 ni MSB kama inavyoonyeshwa kwenye Kielelezo 13.

LUT4 imewekwa kama XOR wakati LUT8 hufanya mantiki ya AND-XOR ya Kielelezo 12.

Matokeo ya kukabiliana na kwenda kwenye pini tatu za pato la dijiti kushughulikia Analog Multiplexer ya nje.

LUT10 huamua nambari ya kaunta wakati skanisho imekamilika na kulisha mapigo kwa Matrix0 kupitia DLY8 na bandari P12. Hii inakamilishwa tu na NA-kuingiza matokeo ya kaunta, kwa hivyo kusimba nambari ya 7 dec (0b111 binary, mwisho wa kitanzi).

Hatua ya 10: Usanidi wa Kifaa - 3-bit Linganisha Logic

Kielelezo 15 kinaonyesha mzunguko unaotumiwa kugundua wakati kitanzi kinazunguka kwenye anwani ya sasa ya "mshindi". Katika kesi hii, kama ilivyojadiliwa tayari, mapigo ya dijiti yanapaswa kulazimisha kupakia tena matokeo ya sasa ya ADC ili kusuluhisha hali inayoweza kutokea.

Anwani ya "mshindi" imehifadhiwa kwenye rejista ya muda ya Matrix1 (tazama hapa chini), wakati anwani ya sasa inatolewa na kaunta ya binary.

Malango ya XNOR hutoa pato la kweli (mantiki 1 au 'juu') wakati pembejeo zote mbili ni sawa. NA-ing ishara hii kwa bits zote (LUT9) hutupa pigo wakati nambari zote mbili za binary zinafanana. Maelezo kuhusu milango ya XOR kama kikagua usawa inaweza kupatikana katika Rejea.

Ishara ya 'Counter-equals-Latch' imepitishwa kwa Matrix0 kupitia bandari P11.

Hatua ya 11: Usanidi wa Kifaa - Mlinganisho wa Dijitali na Usajili wa Muda

Sehemu ya chini ya Kielelezo 11 (iliyoangaziwa kwenye Kielelezo 16) inaonyesha kizuizi cha DCMP, sehemu ya kufanya uamuzi wa muundo huu.

DFF6, 7, na 8 huunda rejista ya 3-bit ili kuhifadhi nambari ya pembejeo ya "mshindi" wakati kitanzi kinaendelea. Ingizo kwa Flip-Flops ni matokeo ya kaunta ya 3-bit, kama inavyoonekana katika mzunguko wa Matrix1 wa Kielelezo 11, hapa imerukwa kwa sababu ya uwazi.

Matokeo ya rejista hii hayawezi kuendesha moja kwa moja onyesho la sehemu 7 kwa sababu thamani iliyohifadhiwa hapa inabadilika wakati wa skana na inapaswa kuzingatiwa kuwa "halali" tu mwisho wa skana yenyewe.

Kwa sababu hii, matokeo ya daftari la muda huunganisha kwenye Usajili wa Kitanzi cha Matrix0 kupitia bandari za baina ya tumbo P13, P14, na P15.

Ni muhimu kuzingatia kwenye Kielelezo 16 kuwa rejista ya muda imefungwa na pato la DCMP OUT + wakati ADC-SPI inasajili matokeo ya kulinganisha katika upeo mpya kupatikana.

Ishara hiyo hiyo ya OUT + imepitishwa kwa Matrix0, SPI CLK Logic, kupitia bandari P10.

Hatua ya 12: Usanidi wa Kifaa - Sifa za Vipengele vya Matrix1

Takwimu 17-19 zinaonyesha vifaa mali ya mali ya Matrix1.

Hatua ya 13: Matokeo

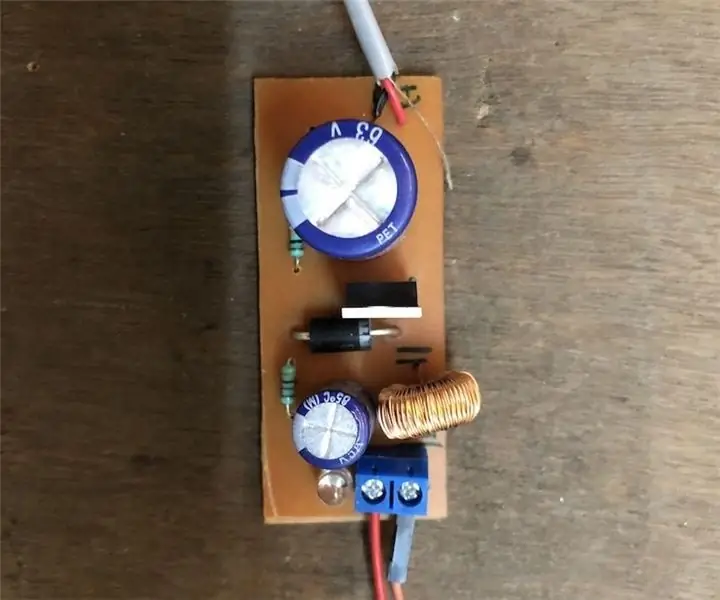

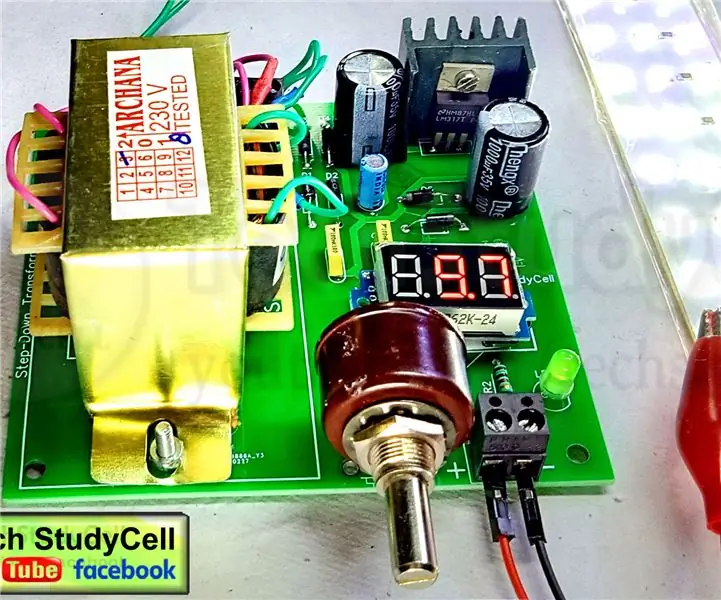

Ili kujaribu utekelezaji, mfano wa bodi ya tathmini umejengwa, ambapo voltages 8 za pembejeo za analog hupatikana na safu ya wagawanyaji wa kontena na TrimPots (kama inavyoonyeshwa kwenye Kielelezo 20).

Multiplexer inayotumiwa ni ADG508, sehemu ambayo inaweza kufanya kazi na usambazaji mmoja (12 V).

Sehemu ya dereva wa sehemu 7 ni 74LS47. Inabainisha neno linalofanana la kuingiza na huendesha moja kwa moja onyesho la kawaida-sehemu 7 ya sehemu.

Bodi ya tathmini ina kontakt 2x10 ya pembe ya kulia ili kuziba moja kwa moja kwenye Jukwaa la Maendeleo ya Juu la GreenPAK kwenye kiunganishi cha upanuzi kama inavyoonyeshwa kwenye Kielelezo 21.

Kuungana na Jukwaa la Maendeleo ya Juu la GreenPAK hufanya iwe rahisi sana kuchukua vipimo vya ishara kwa ukaguzi wa haraka. Kwa mfano, Kielelezo 22 kinaonyesha seti ya ishara (mtawaliwa CLOCK, pato la ADC INT, na DCMP OUT + pato) kama ilivyonaswa na HP 54620A Logic Analyzer. Mifumo ya mawimbi husababishwa na kuongezeka kwa ishara ya OUT + (kwenye wigo ulioitwa 'A> B'), kwa hivyo hii ni kukamata fomu ya wimbi wakati Voltage mpya ya max inagunduliwa kati ya pembejeo za analog. Kwa kweli, ilipatikana kwa kuzungusha moja ya TrimPots ya Bodi ya Tathmini ili kuongeza voltage inayofanana inayoonyeshwa kwenye Kielelezo 22.

Kielelezo 23 kinaonyesha muundo wa Bodi ya Tathmini.

Hitimisho

Katika hii Inayoweza kufundishwa, tulitekeleza kipataji cha voltage cha njia-nane (au min) cha voltage kutumika kama nyongeza ya kawaida kwa mifumo ya udhibiti wa njia nyingi. Njia iliyowasilishwa hutumia huduma za hali ya juu za vifaa vya GreenPAK na inaonyesha jinsi inavyowezekana kujumuisha katika analog moja ya chip na kazi za dijiti. IC kadhaa za kibiashara zinaweza kubadilishwa na Dialog GreenPAKs ili saizi ya programu na gharama zipunguzwe.

Ilipendekeza:

WADAU WA VOLTAGE VOLTAGE 78XX: 6 Hatua

WADHIBITI WA VOLTAGE 78XX: Hapa tungependa kukuonyesha jinsi ya kufanya kazi na wasimamizi wa voltage ya 78XX. Tutaelezea jinsi ya kuziunganisha kwenye mzunguko wa nguvu na ni nini mapungufu ya kutumia vidhibiti vya voltage. Hapa tunaweza kuona vidhibiti vya: 5V, 6V, 9V, 12V, 18V, 24V

Ufuatiliaji wa Voltage kwa Batri za Voltage za Juu: Hatua 3 (na Picha)

Ufuatiliaji wa Voltage kwa Batri za Voltage za Juu: Katika mwongozo huu nitakuelezea jinsi nilivyojenga mfuatiliaji wangu wa voltage ya betri kwa bodi yangu ndefu ya umeme. Weka hiyo hata hivyo unataka na unganisha waya mbili tu kwenye betri yako (Gnd na Vcc). Mwongozo huu ulidhani kuwa voltage yako ya betri huzidi volt 30, w

DC - DC Voltage Hatua ya Kubadilisha Njia ya Buck Voltage Converter (LM2576 / LM2596): Hatua 4

DC - DC Voltage Hatua ya Kubadilisha Njia ya Buck Voltage Converter (LM2576 / LM2596): Kufanya ubadilishaji mzuri wa pesa ni kazi ngumu na hata wahandisi wenye uzoefu wanahitaji miundo mingi kuja kwa moja ya haki. ni kibadilishaji umeme cha DC-to-DC, ambacho hupunguza voltage (wakati unazidi

Usambazaji wa Nguvu ya Voltage DC inayoweza Kurekebishwa Kutumia Udhibiti wa Voltage LM317: Hatua 10

Usambazaji wa Nguvu ya Voltage DC inayoweza Kurekebishwa Kutumia Udhibiti wa Voltage ya LM317: Katika mradi huu, nimeunda umeme rahisi wa umeme wa DC kwa kutumia LM317 IC iliyo na mchoro wa mzunguko wa usambazaji wa umeme wa LM317. Kwa kuwa mzunguko huu una kisanifu cha daraja kilichojengwa ili tuweze kuunganisha moja kwa moja usambazaji wa ACV / 110V kwa pembejeo.

Picaxe Kulingana na kipima joto cha dijiti na Max na Min: Hatua 13

Pimaxe Inayotokana na Kipimajoto cha dijiti na Max na Min: (Tafadhali acha ujumbe, lakini usiwe wa kukosoa sana, hii ni mafundisho yangu ya kwanza! Inategemea chip ya Picaxe kwani ni ya bei rahisi na rahisi kutumia. Ikiwa hii ni ya